Stellenausschreibung

-

Wissenschaftliche/r Mitarbeiter/in (m/w/d) im Fachgebiet Architekturen und Systemeim Rahmen eines Verbundprojektes sind am Institut für Mikroelektronische Systeme mehrere Stellen als Wissenschaftliche/r Mitarbeiter/in (m/w/d) im Fachgebiet Architekturen und Systeme (EntgGr. 13 TV-L, 100%) zum 01.04.2023 oder später zu besetzen. Die Stellen sind zunächst jeweils auf 3 Jahre befristet und bieten die Möglichkeit zur Promotion.Betreuung: Prof. Dr.-Ing. Holger BlumeJahr: 2023

Großes Projekt

-

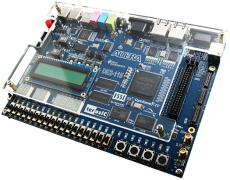

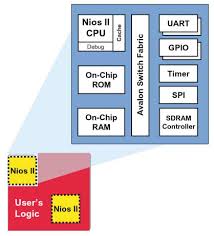

Echtzeitbetriebssystem für FPGA-basierten BUS-ControllerFür die echtzeitfähige Steuerung eines komplexen physikalischen Experiments soll das Echtzeitbetriebssystem RTEMS-5 auf einen Intel SoC-FPGA-basierten BUS-Controller portiert werden. Dafür muss ein Board-Support-Package erstellt werden, sowie vorhandene Linux-Treiber und Anwendungen portiert werden.Betreuung: Spindeldreier, ChristianStudent/in:Jahr: 2018Laufzeit: 15.10.2018-

![]()

![]()

-

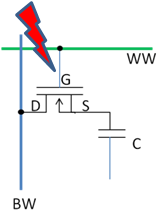

Zero Voltage DetectionIm Rahmen der Seminararbeit wird eine integrierte Zero-Voltage-Detection-Schaltung zur Unterstützung von Zero Voltage Switching eines Wechselrichters in einer Hochvolttechnologie designed und ausgelegt. Der Fokus liegt dabei auf einer hohen Robustheit gegenüber steilen Schaltflanken und den damit verbundenen Gleichtaktstörungen. Außerdem wird ein Layout der Schaltung erstellt.Betreuung: Christoph HillmerStudent/in:Jahr: 2021Laufzeit: 19.04.2021-19.10.2021

-

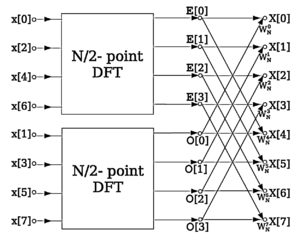

Implementierung eines Echtzeit-Demonstrators für eine Computed Order Tracking AnwendungBetreuung: Jens Karrenbauer, M.Sc.Jahr: 2022

-

Entwurf einer Delay Locked Loop mit erweitertem FrequenzbereichIn dieser Arbeit wurde eine Delay Locked Loop (DLL) in einem integrierten 55nm Prozess entwickelt, die einen besonders großen Frequenzbereich unterstützt.Betreuung: Ferdinand PieperStudent/in:Jahr: 2023Laufzeit: 01.04.2023 – 31.08.2023

Hiwi-Tätigkeit

-

VHDL-Implementierung eines Videokamera-TreibersZum Aufbau eines Live-Demonstrators soll ein Treibermodul zur Ansteuerung einer Videokamera-Einheit auf einem DE2-115 FPGA-Board implementiert werden.

![]()

![]()

-

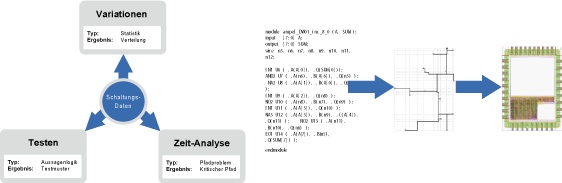

MATLAB-Implementierung für einen Ansatz zur automatisierten Verifikation von analogen SchaltungenEs soll eine Implementierung zur Erzeugung von verifikationsgerechten Verhaltensmodellen analoger Schaltungen in MATLAB umgesetzt werden.

![]()

![]()

-

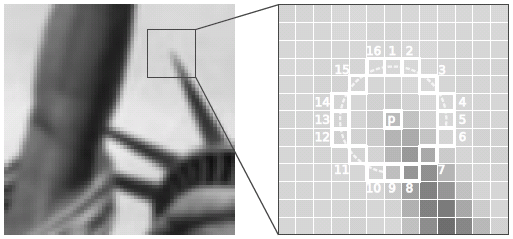

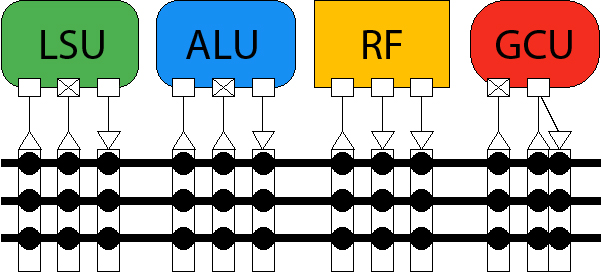

Extraktion von lokalen Bildmerkmalen auf angepassten ASIP-ArchitekturenZur beschleunigten Extraktion von lokalen Bildmerkmalen sollen ASIP-Befehlssatzerweiterungen entwickelt werden. In diesen Arbeiten wird evaluiert, welche Beschleunigung der Algorithmen bei gleichzeitiger Prozessorflexibilität möglich ist. Die Ergebnisse finden Anwendung in Algorithmen- und Prozessor-spezifischen Modellen.

![]()

![]()

-

Entwicklung eines objektorientierten Software-Tools zur Modifikation und Informationsextraktion aus ASIC-GatternetzlistenFür das DFG-geförderte Projekt „Quantification of the Trade-off between Energy and Exactness in Computer Vision Processor Architectures Enhanced with Stochastic Computing Mechanisms“ soll im Rahmen einer HiWi-Tätigkeit ein Software-Tool entwickelt werden, welches Schaltungsinformation aus Gatternetzlisten extrahiert, diese in eine objektorientierte Darstellung überführt und diese modifizierbar bzw. instrumentierbar macht.Betreuung: Weißbrich, MoritzStudent/in:

![]()

![]()

-

Implementierung approximierender arithmetischer Einheiten für Prozessoren mit Datenpfad-PipeliningIn der Literatur werden Ansätze und Konzepte für approximierende Einheiten vorgestellt, die zumeist auf rein kombinatorischen Schaltungen basieren. Sollen diese in Prozessoren mit einem aus mehreren Pipelinestufen bestehenden Datenpfad verwendet werden, so ergeben sich unterschiedliche Möglichkeiten, das Pipelining zu realisieren. Dies kann Auswirkungen auf die Fehlercharakteristik der Näherungsergebnisse zeigen. Für die Untersuchung der genannten Zusammenhänge sollen in einer HiWi-Tätigkeit approximierende arithmetische Einheiten in der Hardware-Beschreibungssprache VHDL implementiert werden, die zur Anwendung eines parametrisierbaren Pipelining-Schemas geeignet sind.Betreuung: Weißbrich, MoritzStudent/in:

![]()

![]()

-

Software-Entwicklung im Bereich physikalischer Entwurf

-

Software-EntwicklungStudent/in:Jahr: 2009Laufzeit: 14.01.2008-01.04.2009

-

Programmierung einer FSM-basierten Netzwerkprozessor-EinheitStudent/in:Jahr: 2009Laufzeit: 01.11.2008-30.11.2009

-

Software-EntwicklungStudent/in:Jahr: 2009Laufzeit: 01.11.2008-31.10.2009

-

Software-EntwicklungStudent/in:Jahr: 2009Laufzeit: 01.03.2009-31.05.2009

-

DSP-ProgrammierungStudent/in:Jahr: 2009Laufzeit: 01.02.2009-30.10.2009

-

Musikklassifikation mit MatlabStudent/in:Jahr: 2009Laufzeit: 30.07.2009-30.09.2009

-

GPU beschleunigte MusikklassifikationStudent/in:Jahr: 2009Laufzeit: 01.09.2009-30.11.2009

-

Software-EntwicklungStudent/in:Jahr: 2009Laufzeit: 01.10.2009-

-

Software-EntwicklungStudent/in:Jahr: 2009Laufzeit: 01.10.2009-31.12.2009

-

Grundlagen digitaler SystemeBetreuung: Payá Vayá, GuillermoStudent/in:Jahr: 2010Laufzeit: 01.10.2007-01.11.2010

-

Software-EntwicklungStudent/in:Jahr: 2010Laufzeit: 01.06.2010-01.07.2010

-

LaborbetreungStudent/in:Jahr: 2010Laufzeit: 01.10.2008-20.12.2010

-

Software-EntwicklungStudent/in:Jahr: 2010Laufzeit: 01.04.2009-11.06.2010

-

Approximation elementarer Funktionen in Fließ- und FestkommaarithmetikStudent/in:Jahr: 2010Laufzeit: 31.01.2010

-

Entwicklung und Evaluation grundlegender Bildverarbeitungsalgorithmen auf ASIP und CUDAStudent/in:Jahr: 2010Laufzeit: 01.12.2009-11.04.2010

-

Software-Entwicklung im Bereich physikalischer EntwurfStudent/in:Jahr: 2010Laufzeit: 02.12.2010-02.12.2010

-

Software-EntwicklungStudent/in:Jahr: 2011Laufzeit: 01.10.2007-01.08.2011

-

Entwicklung einer Java Anwendung zur Datenvisualisierung auf einer BlackBerry-PlattformStudent/in:Jahr: 2011Laufzeit: 30.09.2009-30.09.2011

-

DSP-ImplementierungStudent/in:Jahr: 2011Laufzeit: 01.11.2009-01.08.2011

-

Grundlagen digitaler SystemeStudent/in:Jahr: 2011Laufzeit: 15.10.2009-25.03.2011

-

Software-EntwicklungStudent/in:Jahr: 2011Laufzeit: 01.06.2009-30.06.2011

-

Entwicklung einer Matlab GUIStudent/in:Jahr: 2011Laufzeit: 06.05.2010-14.09.2011

-

Programmiertools für einen FSM-basierten ProzessorStudent/in:Jahr: 2011Laufzeit: 01.06.2010-31.01.2011

-

Betreuung des Labors FPGA EntwurfstechnikStudent/in:Jahr: 2011Laufzeit: 20.10.2010-04.02.2011

-

Betreuung des Labors FPGA EntwurfstechnikStudent/in:Jahr: 2011Laufzeit: 20.10.2010-04.02.2011

-

Software-Entwicklung zur Optical-Flow-BerechnungStudent/in:Jahr: 2011Laufzeit: 01.12.2010-01.02.2011

-

SW-EntwicklungStudent/in:Jahr: 2011Laufzeit: 01.01.2011-30.06.2011

-

Software-Entwicklung im Bereich physikalischer EntwurfStudent/in:Jahr: 2011Laufzeit: 16.11.2010-01.10.2011

-

C-Implementierung SURF Merkmalserkennung und VerarbeitungStudent/in:Jahr: 2011Laufzeit: 01.03.2011-29.04.2011

-

Datensatzerweiterung FußgängererkennungStudent/in:Jahr: 2011Laufzeit: 01.08.2011-01.11.2011

-

Gruppenübung zu "Grundlagen digitaler Systeme"Student/in:Jahr: 2011Laufzeit: 01.10.2011-31.12.2011

-

Gruppenübung zu "Grundlagen digitaler Systeme"Student/in:Jahr: 2011Laufzeit: 01.10.2011-31.12.2011

-

Gruppenübung zu "Grundlagen digitaler Systeme"Student/in:Jahr: 2011Laufzeit: 01.10.2011-31.12.2011

-

Software-EntwicklungStudent/in:Jahr: 2011Laufzeit: 15.10.2011-

-

Implementierung von Algorithmen zur digitalen Signalverarbeitung in drahtlosen MIMO OFDM KommunikationssystemenBetreuung: Kock, MarkusStudent/in:Jahr: 2012Laufzeit: 01.04.2012-

-

Implementierung und Optimierung einer echtzeitfähigen Soundsynthese auf Basis des NIOS II ProzessorsStudent/in:Jahr: 2012Laufzeit: 15.04.2012-15.09.2012

-

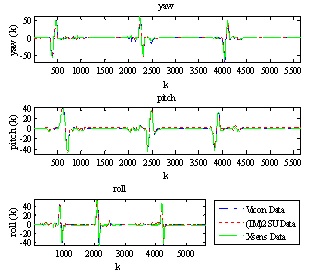

Implementierung von Algorithmen zur Sensordatenfusion von InertialsensorenImplementierung und Latenz- und Genauigkeitsanalyse verschiedener Sensorfusions-Algorithmen für InertialsensorenStudent/in:Jahr: 2012Laufzeit: 15.08.2012-

![]()

![]()

-

Softwareentwicklung im Projekt AMVStudent/in:Jahr: 2012Laufzeit: 30.11.2012

-

Entwicklung einer Auswerteeinheit für medizinische Sensordaten mit C++ & QtStudent/in:Jahr: 2012Laufzeit: 01.11.2012-

-

Entwicklung eines flexibel erweiterbaren C-nach-Assembler Übersetzers für einen konfigurierbaren VLIW-SIMD-ProzessorStudent/in:Jahr: 2012Laufzeit: 01.11.2012-

-

Betreuung des Labors FPGA EntwurfstechnikStudent/in:Jahr: 2012Laufzeit: 01.10.2011-27.01.2012

-

Entwicklung eines Demonstrationssystems zur Sonifikation von BewegungsdatenStudent/in:Jahr: 2012Laufzeit: 15.10.2010-03.05.2012

-

Programmierung einer GUI zur Steuerung eines FPGA-basierten Audio-EffektgerätsIm Rahmen dieser Tätigkeit wird eine grafische Benutzeroberfläche zur Steuerung eines FPGA-basierten Audio-Effektgeräts implementiert.Student/in:Jahr: 2012Laufzeit: 28.05.2014-

![]()

![]()

-

Entwicklung eines echtzeitfähigen Regelungs-Systems für die orthopädische RehabilitationStudent/in:Jahr: 2012Laufzeit: 06.05.2010-30.04.2012

-

Darstellung von MerkmalsräumenStudent/in:Jahr: 2012Laufzeit: 20.10.2010-02.11.2012

-

Entwicklung eines RFID-LeseadaptersZiel ist es einen RFID-Leser unter Nutzung einer am Insittut vorhandenen Plattform aufzubauenStudent/in:Jahr: 2012Laufzeit: 02.05.2011-30.09.2012

-

Betreuung des Erstsemesterlabors 2011/2012Betreuung: Cholewa, FabianStudent/in:Jahr: 2012Laufzeit: 01.11.2011-31.01.2012

-

Untersuchung der Auswirkungen von Merkmalsquantisierungen auf die MusikklassifikationStudent/in:Jahr: 2012Laufzeit: 16.05.2011-02.11.2012

-

VHDL-Modul zur Ansteuerung eines SensorsystemsStudent/in:Jahr: 2012Laufzeit: 01.07.2011-31.12.2012

-

GUI-Programmierung zur Musikdatenbank-AnalyseStudent/in:Jahr: 2012Laufzeit: 01.06.2011-02.11.2012

-

Betreuung des Labors FPGA EntwurfstechnikStudent/in:Jahr: 2012Laufzeit: 01.10.2011-07.02.2012

-

Betreuung des Erstsemesterlabors 2011/2012Betreuung: Cholewa, FabianStudent/in:Jahr: 2012Laufzeit: 01.11.2011-31.01.2012

-

Betreuung des Erstsemesterlabors 2011/2012Betreuung: Cholewa, FabianStudent/in:Jahr: 2012Laufzeit: 01.11.2011-31.01.2012

-

Betreuung des Erstsemesterlabors 2011/2012Betreuung: Cholewa, FabianStudent/in:Jahr: 2012Laufzeit: 01.11.2011-31.01.2012

-

Betreuung des Erstsemesterlabors 2011/2012Betreuung: Cholewa, FabianStudent/in:Jahr: 2012Laufzeit: 01.11.2011-31.01.2012

-

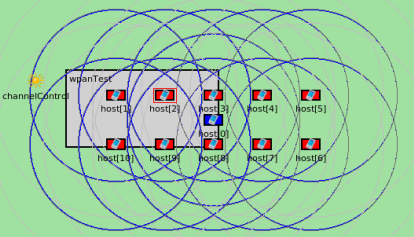

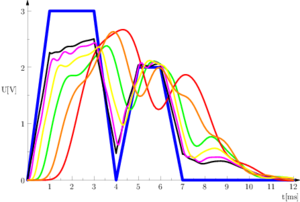

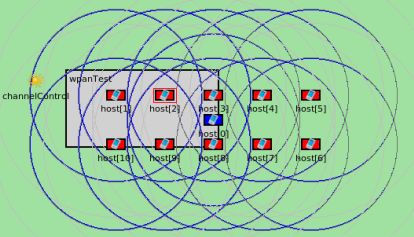

Implementierung von energieeffizienten Routingprotokollen für den Simulator OmNet++Aufgabe ist die Implementierung von energieeffizienten Routingprotokollen für den Netzwerksimulator OMNet++ unter Nutzung des MiXiM-FrameworksStudent/in:Jahr: 2013Laufzeit: 03.10.2011-02.02.2013

-

Implementierung des Medienzugriffsverfahrens RI-MAC für den Simulator OmNet++Implementierung des Medienzugriffsverfahrens RI-MAC für den Simulator OMNet++ unter Nutzung des MiXiM-FrameworksStudent/in:Jahr: 2013Laufzeit: 01.10.2011-01.01.2013

-

Konstruktion einer Braille-UhrStudent/in:Jahr: 2013Laufzeit: 01.02.2012-28.02.2013

-

FahrerassistenzalgorithmenStudent/in:Jahr: 2013Laufzeit: 15.03.2012-30.09.2013

-

Erstellung eines programmierbaren Moduls für das FPGA-LaborStudent/in:Jahr: 2013Laufzeit: 20.08.2012-31.03.2013

-

Gruppenübung zu "Grundlagen digitaler Systeme"Student/in:Jahr: 2013Laufzeit: 15.10.2012-31.01.2013

-

Betreuung FPGA-Labor 2012/2013Student/in:Jahr: 2013Laufzeit: 01.10.2012-31.01.2013

-

Betreuung FPGA-Labor 2012/2013Student/in:Jahr: 2013Laufzeit: 01.10.2012-31.01.2013

-

Betreuung FPGA-Labor 2012/2013Student/in:Jahr: 2013Laufzeit: 01.10.2012-31.01.2013

-

Softwareentwicklung im Projekt AMVStudent/in:Jahr: 2013Laufzeit: 31.10.2013

-

Betreuung Miniprojekt SchaltungsentwurfStudent/in:Jahr: 2013Laufzeit: 14.03.2013

-

Tutor der Gruppenübung zur Vorlesung "Elektrotechnische Grundlagen der Informationstechnik/Informatik"Student/in:Jahr: 2013Laufzeit: 31.12.2013

-

Softwareentwicklung im Projekt AMVStudent/in:Jahr: 2013Laufzeit: 30.05.2013

-

Betreuung Miniprojekt SchaltungsentwurfStudent/in:Jahr: 2013Laufzeit: 14.03.2013

-

VHDL Implementierungen für Hörgeräte-AlgorithmenBetreuung: Seifert, ChristopherStudent/in:Jahr: 2013Laufzeit: 30.04.2013-

-

Verifikation eines IEEE 802.15.4-SimulationsmodellsVerifikation eines IEEE 802.15.4-Simulationsmodells für das Netzwerksimulationsframework OMNeT++Student/in:Jahr: 2013Laufzeit: 01.08.2013-

![]()

![]()

-

Grundlagenlabor CMOSBetreuung: Kock, MarkusStudent/in:Jahr: 2013Laufzeit: 01.08.2013-

-

Implementierung und Evaluation eines Multikanal-Audio-Treibers zur Verwendung unter Linux auf dem ZedboardBetreuung: Seifert, ChristopherStudent/in:Jahr: 2013Laufzeit: 15.10.2013-

-

Betreuung des Schaltungsentwurfs beim Projekt Technische InformatikJahr: 2013Laufzeit: 18.03.2013-17.04.2013

-

C++ GUI Design mit QTStudent/in:Jahr: 2013Laufzeit: 01.08.2013-31.10.2013

-

Implementierung und Optimierung von Algorithmen zur BewegungssonifikationJahr: 2013Laufzeit: 28.09.2011-15.03.2013

-

Betreuung des Erstsemesterlabors 2012/2013Betreuung: Cholewa, FabianStudent/in:Jahr: 2013Laufzeit: 01.11.2011-31.01.2013

-

MATLAB-Implementierung für einen Ansatz zur automatisierten Verifikation von analogen SchaltungenEs soll eine Implementierung zur Erzeugung von verifikationsgerechten Verhaltensmodellen analoger Schaltungen in MATLAB umgesetzt werden.Student/in:Jahr: 2014Laufzeit: 01.10.2014-

![]()

![]()

-

Implementierung von Algorithmen zur digitalen Signalverarbeitung in drahtlosen MIMO OFDM KommunikationssystemenBetreuung: Kock, MarkusStudent/in:Jahr: 2014Laufzeit: 29.11.2012-30.06.2014

-

Sonifikations-Demonstrator auf Basis des Altera Nios IIStudent/in:Jahr: 2014Laufzeit: 01.03.2013-28.02.2014

-

Software-EntwicklungStudent/in:Jahr: 2014Laufzeit: 24.04.2008-01.04.2014

-

Software-EntwicklungStudent/in:Jahr: 2014Laufzeit: 24.03.2008-01.04.2014

-

Arbeiten am Chipdesign Performance Management SystemStudent/in:Jahr: 2014Laufzeit: 01.01.2009-01.04.2014

-

Gruppenübung zu "Grundlagen digitaler Systeme"Student/in:Jahr: 2014Laufzeit: 01.11.2013-31.01.2014

-

Gruppenübung zu "Grundlagen digitaler Systeme"Student/in:Jahr: 2014Laufzeit: 15.10.2013-31.01.2014

-

Erarbeitung und Verifikation eines Verlustleistungsmodells für den Tensilica Xtensa LX4Im Rahmen der Forschungsarbeiten zur Verlustleistungsmodellierung soll für den Tensilica Xtensa LX4 ein entsprechendes Verlustleistungsmodell für die Emulation auf FPGAs erarbeitet werden.Student/in:Jahr: 2014Laufzeit: 07.02.2014-

-

MOAI4K2_ASM v2.0Konzeptionierung und Implementierung einer erweiterten Version des Instruction Schedulers für den MOAI ProzessorStudent/in:Jahr: 2014Laufzeit: 01.02.2014-

-

Implementierung von Audio-Algorithmen zur Rückkopplungsunterdrückung in digitalen HörgerätenAudio-Algorithmen zur Rückkopplungsunterdrückung in digitalen Hörgeräten werden in MATLAB implementiert und evaluiert. Anschließend werden diese Algorithmen für verschiedene Architekturen portiert und durch Messungen getestet.Betreuung: Gerlach, LukasStudent/in:Jahr: 2014Laufzeit: 01.03.2014-

![]()

![]()

-

Programmierarbeiten in Java und Optimierung von Design-Prozessen anhand von AbhängigkeitsgraphenStudent/in:Jahr: 2014Laufzeit: 03.08.2009-01.04.2014

-

Betreuung ErstsemesterlaborBetreuung: Cholewa, FabianStudent/in:Jahr: 2014Laufzeit: 04.03.2014-

-

Betreuung ErstsemesterlaborBetreuung: Cholewa, FabianStudent/in:Jahr: 2014Laufzeit: 04.03.2014-

-

Betreuung ErstsemesterlaborBetreuung: Cholewa, FabianStudent/in:Jahr: 2014Laufzeit: 04.03.2014-

-

Betreuung ErstsemesterlaborBetreuung: Cholewa, FabianStudent/in:Jahr: 2014Laufzeit: 04.03.2014-

-

Low-Overhead Thermal SensorsStudent/in:Jahr: 2014Laufzeit: 17.03.2014-30.04.2014

-

Tutor der Gruppenübung zur Vorlesung "Elektrotechnische Grundlagen der Informationstechnik/Informatik"Student/in:Jahr: 2014Laufzeit: 01.04.2014-14.11.2014

-

Programmierarbeiten am Chipdesign Performance Management SystemStudent/in:Jahr: 2014Laufzeit: 01.10.2009-01.04.2014

-

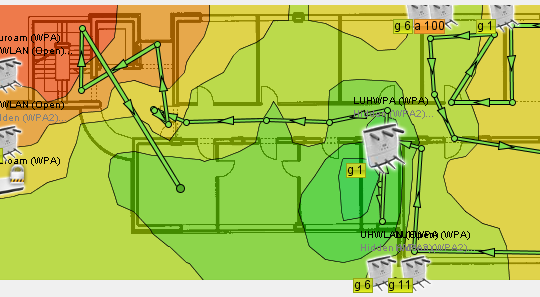

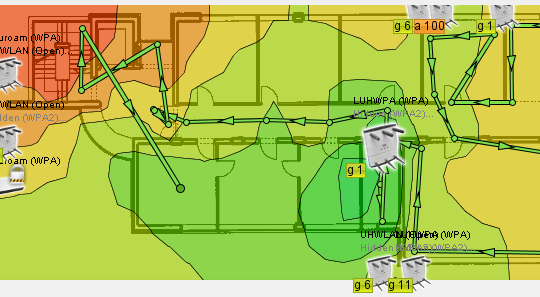

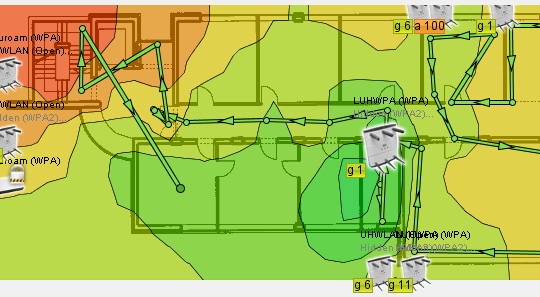

Site Survey ToolAufgabe ist es ein Programm zur Unterstützung von Funkdämpfungsmessungen innerhalb von Gebäuden zu erstellen.Student/in:Jahr: 2014Laufzeit: 01.01.2014-

![]()

![]()

-

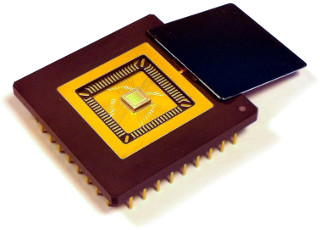

Inbetriebnahme einer Lab-on-Chip-Systems zur Vermessung von BiofilmenZur Vermessung und Untersuchung von Biofilmen sollen spezielle Lab-on-Chip-Systeme eingesetzt werden. Die ermöglichen es, Biofilme direkt auf Kontaktflächen zu Sensoren zu kultivieren und über die Zeit vermessen zu können.Student/in:Jahr: 2014Laufzeit: 28.05.2014-15.08.2014

![]()

![]()

-

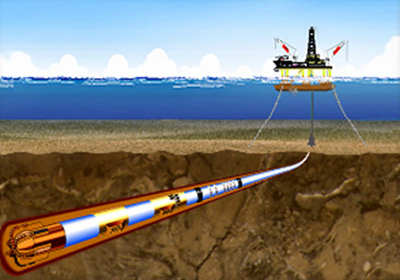

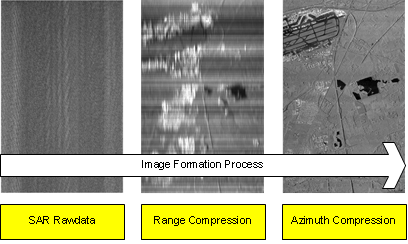

Unterstützung bei der Hard- und Softwareentwicklung für die Echtzeit SAR-BilddatenverarbeitungBackprojektion-Verfahrensanalyse (MATLAB), Entwicklung von VHDL Modulen (Debugging, Funktionstest, Integration) Demonstratoraufbau (FMCW Sensor mit Linearführugsschiene)Betreuung: Cholewa, FabianStudent/in:Jahr: 2014Laufzeit: 01.06.2014-

-

Implementierung einer GUI für eine MWD-EmulationsplattformAs a result of ongoing research on high temperature electronics in drilling applications, an adapted processor architecture has been elaborated. In order to verify the functionality of the design, a demonstration platform is being set up. On that platform, sensor samples can be applied and processed by the proposed architecture. The objective of the assisting work is to capture digitalized sensor data from an IMU-System, to store these samples in the emulation platform, to transfer to a host PC and to display the measured values.Student/in:Jahr: 2014Laufzeit: 01.01.2014-30.09.2014

![]()

![]()

-

Statische Analysen am CDFG des GCCStudent/in:Jahr: 2014Laufzeit: 29.08.2011-25.05.2014

-

Design und Implementierung einer grafischen Oberfläche zur Steuerung digitaler Hörgeräte über BluetoothIm Rahmen einer Hiwi-Tätigkeit soll eine grafische Oberfläche für ein Tablet entworfen und implementiert werden. Das Ziel ist eine Kommunikation zwischen dem Tablet und den am Institut entwickelten Hörgeräteplattformen zur Steuerung und Analyse der Audiosignalverarbeitung.Betreuung: Gerlach, LukasJahr: 2015

![]()

![]()

-

Design und Implementierung einer grafischen Oberfläche zur Steuerung digitaler Hörgeräte über BluetoothIm Rahmen einer Hiwi-Tätigkeit soll eine grafische Oberfläche zur Steuerung eines Hörgerätesystems per Bluetooth implementiert werden.Betreuung: Gerlach, LukasStudent/in:Jahr: 2015Laufzeit: 15.04.2015-14.07.2015

![]()

![]()

-

Software-Entwicklung zur Durchführung einer beschleunigten Analog/Mixed-Signal SimulationStudent/in:Jahr: 2015Laufzeit: 01.12.2015-

![]()

![]()

-

Tutor der Gruppenübung zur Vorlesung "Elektrotechnische Grundlagen der Informationstechnik/Informatik"Student/in:Jahr: 2015Laufzeit: 01.04.2014-31.03.2015

-

Mitentwicklung am Projekt ROBUSTJahr: 2015

-

Implementierung und Evaluation eines Spracherkennungsalgorithmus auf einem VLIW-SIMD SignalprozessorEin Spracherkennungsalgorithmus wird implementiert und evaluiert werden. Die zu evaluierende Prozessorarchitektur ist der am diesem Institut entwickelte VLIW-SIMD Signalprozessor.Betreuung: Gerlach, LukasStudent/in:Jahr: 2016Laufzeit: 01.12.2015-29.02.2016

![]()

![]()

-

Evaluation der Leistungsfähigkeit eines VLIW-SIMD Signalprozessors für Speech-Enhancement-AlgorithmenEin Speech-Enhancement-Algorithmus wird in dieser Arbeit implementiert und evaluiert. Die zu evaluierende Prozessorarchitektur ist ein am diesem Institut entwickelter VLIW-SIMD Signalprozessor.Betreuung: Gerlach, LukasStudent/in:Jahr: 2016Laufzeit: 01.12.2015-29.02.2016

![]()

![]()

-

Implementierung einer Schnittstelle um die Erweiterung einer bestehenden Simulationsumgebung in MATLAB/Simulink-UmgebungBetreuung: Divanbeigi, SaraStudent/in:Jahr: 2016

![]()

![]()

-

Betreuer von Programmierprojekt: Electronic Design AutomationBetreuung: Divanbeigi, Sara; Rechmal, MalgorzataStudent/in:Jahr: 2016

![]()

![]()

-

Softwareentwicklung im Projekt AMVJahr: 2017

-

Entwurf eines Tools zur automatisierten Erzeugung von Trainingsdaten für Support Vector MachinesJahr: 2017

-

Implementierung von Optimierungsalgorithmen für das Training von Support Vector MachinesJahr: 2017

-

Betreuer von Programmierprojekt: Electronic Design AutomationBetreuung: Divanbeigi, Sara; Rechmal, MalgorzataStudent/in:Jahr: 2017Laufzeit: 01.01.2017-

![]()

![]()

-

FPGA Labor TutorBetreuung von Studierenden Gruppen im Rahmen des Labors FPGA EntwurfstechnikBetreuung: Stanislawski, Nils Hendrik; Spindeldreier, ChristianJahr: 2017Laufzeit: 01.08.2017-

![]()

![]()

-

Gruppenübungsleiter/innen gesuchtEs ist noch eine Stelle als Gruppenübungsleiter für die Veranstaltung "Grundlagen digitaler Systeme" zu vergeben.Betreuung: Seifert, ChristopherJahr: 2018

-

Konzeption, Aufnahme und Schnitt von Videodaten für die LehreBei der dieser Tätigkeit geht es um die Konzeptionierung und Aufnahme von Videos, welche begleitend zu Vorlesung und Übung den Studenten helfen soll die schwierigen Inhalte zu verstehen.Betreuung: Stuckenberg, TobiasStudent/in:Jahr: 2018Laufzeit: 01.04.2018-30.09.2018

![]()

![]()

-

Objektorientierte Programmierung in C++Betreuung: Divanbeigi, SaraJahr: 2018Laufzeit: 22.05.2017-

-

Implementierung von Hardware-Modulen für die Signalverarbeitung auf WeltraummissionenIm Rahmen der Verbundprojekte QUANTUS IV - MAIUS und BECCAL sollen Hardware Module für die digitale Signalverarbeitung auf Weltraummissionen implementiert werden.Betreuung: Spindeldreier, ChristianStudent/in:Jahr: 2018Laufzeit: 01.02.2018-15.12.2018

![]()

![]()

-

Software-Entwicklung im Bereich Analog-DesignBetreuung: Divanbeigi, SaraStudent/in:Jahr: 2019

![]()

![]()

Bachelor-/Studienarbeit

-

Verbesserung der zeitlichen Korrelation eines Verlustleistungsmodells für einen RISC-ProzessorIm Rahmen der Forschungsarbeiten zur Verlustleistungsmodellierung soll ein vorhandenes Modell für die Verlustleistung eines RISC-Prozessors hinsichtlich seiner zeitlichen Korrelation zum Verlustleistungsverlauf der Gatter-Simulation verbessert werden.Student/in:

-

Entwicklung einer Referenzimplementierung zur virtuellen 3D-Rekonstruktion einer Gefäßprothese auf Basis von UltraschallbildernZur Qualitätskontrolle einer wachsenden Gefäßprothese können mit Hilfe der Ultraschallbildgebung Schnittbilder des wachsenden Organs berührungslos aufgenommen werden. Diese Bilder dienen als Eingabe für die 3D-Visualisierung der eigentlich Prothese. Auf Basis dieser Visualisierung können anschließend physikalische Simulationen durchgeführt werden.Student/in:

![]()

![]()

-

Konzeption und Umsetzung eines frequenzbasierten Analyseverfahrens zur Detektion von zeitlichen Flackerartefakten in Videoaufnahmen verursacht durch gepulste LED-LichtquellenIn dieser Bachelorarbeit soll eine Methodik erforscht werden, mit der das Flackern gepulster LED-Scheinwerfer in Videoaufnahmen präzise detektiert werden kann. Mittels eines darauf aufbauenden nachgeschalteten Moduls soll eine Reduktion des Flackerns ermöglicht werden.Betreuung: Behmann, NicolaiStudent/in:

![]()

![]()

-

Entwicklung eines Heizsystems für die Charaktersierung von Hochtemperatur-ASICsUm das Verhalten eines Hochtemperatur-ASICs mit verschiedenen Addierer-Architekturen bei Temperaturen bis 250° C zu erforschen wird ein Heizsystem benötigt. Dabei soll der ASIC gleichmäßig aufgeheizt werden, während die Temperatur der Platine möglichst niedrig bleibt, um das Platinenmaterial nicht zu beschädigen. Das Hauptproblem ist hierbei der Wärmefluss durch die Pins, der das ASIC-Gehäuse abkühlt und die Platine aufheizt.Betreuung: Webering, Fritz; Payá Vayá, GuillermoStudent/in:

![]()

![]()

-

Konzipierung und Implementierung eines drahtlosen Sensor-Netzwerks für medizinische BioreaktorenAm Fachgebiet „Architekturen und Systeme“ des Instituts für Mikroelektronische Systeme werden Projekte zur Konzipierung und Implementierung von Sensorplattformen für medizinische Bioreaktoren durchgeführt. Im Rahmen des Verbundprojekts „Biofabrication for NIFE“ werden Möglichkeiten erforscht, organische Gefäßprothesen autolog zu kultivieren. Am IMS sollen dazu Sensorplattformen zur Überwachung und Kontrolle dieser Kultivie-rungsprozesse realisiert werden. Dabei werden vor allem hohe Anforderungen an die drahtlose Kommunikation in Bezug auf eine sichere Datenübertragung und Zuverlässigkeit gestellt.Betreuung: Stanislawski, Nils HendrikStudent/in:

![]()

![]()

-

Entwicklung, Implementierung und Evaluierung einer Langzeit-Elektrostimulationseinheit für Cochlea-ImplantateDer in dieser Arbeit zu entwickelnde elektronische Teil eines Cochlea-Implantats besteht aus einer (analogen) Audiosignalverarbeitungskette zur Erzeugung elektronischer Stimuli. Als Anforderung an das Design ergeben sich insbesondere eine lange Lebenszeit mit mobiler Stromversorgung sowie die Minimierung von Größe und Gewicht des Systems, um die Belastung der Probanden gering zu halten.Betreuung: Stanislawski, Nils HendrikStudent/in:

![]()

![]()

-

Entwicklung, Implementierung und Evaluierung einer drahtlosen Sensorplattform zur Orientierungs- und PositionsschätzungIm Rahmen dieser Arbeit soll eine drahtlose IMU bzw. MARG Sensorplattform entwickelt werden, indem ein bestehendes IMU Design überarbeitet wird. Dabei ist insbesondere eine Optimierung der Platinengröße, Akkulaufzeit und Drahtlosfunktionalität der IMU durch ein angepasstes Schaltungsdesign und Board-Layout Bestandteil der Aufgabe. Weiterhin sollen verschiedene Algorithmen zur Informationsfusion hinsichtlich ihrer Eignung zur Orientierungs- und Positionsschätzung und ihrer entsprechenden Performance untersucht und verglichen werden.Betreuung: Stanislawski, Nils HendrikStudent/in:

![]()

![]()

-

Entwicklung einer Software für die Kompilierung und Optimierung von Instruktionscode einer FSM-basierten NetzwerkprozessoreinheitStudent/in:Jahr: 2009Laufzeit: 15.01.2009-15.05.2009

-

Evaluation von Ansätzen zur beschleunigten Berechnung linearer Gleichungssysteme mit Hilfe paralleler VerfahrenStudent/in:Jahr: 2009Laufzeit: 18.11.2008-26.05.2009

-

Simulation, Modellierung und Evaluation einer FSM-basierten Netzwerkprozessor-ArchitekturStudent/in:Jahr: 2009Laufzeit: 05.03.2008-27.06.2009

-

Kräftebasiertes Platzierungswerkzeug mit lokal veränderlicher PlatzierungsdichteStudent/in:Jahr: 2009Laufzeit: 29.06.2009-29.12.2009

-

Konzeption und VHDL-Implementierung einer Rektifizierungseinheit für Stereo-Kamera-BilderStudent/in:Jahr: 2009Laufzeit: 11.06.2009-11.12.2009

-

Design und Evaluation eines konfigurierbaren Timeout-Managers als spezialisierte Hardwareeinheit für einen NetzwerkprozessorStudent/in:Jahr: 2009Laufzeit: 08.04.2009-08.10.2009

-

Programmierung, Optimierung und Evaluation einer Mulit-Core-Architektur aus FSM-gesteuerten NetzwerkprozessorkernenStudent/in:Jahr: 2009Laufzeit: 08.04.2009-08.10.2009

-

Entwicklung einer Software für die Optimierung, Analyse, und Anordnung des Instruktionscodes einer FSM-basierten NetzwerkprozessoreinheitStudent/in:Jahr: 2009Laufzeit: 08.06.2009-21.12.2009

-

Konzeption und VHDL-Implementierung einer Hardware-Architektur zur vergleichsbasierten Auswertung von WinkelverteilungsräumenStudent/in:Jahr: 2009Laufzeit: 01.04.2009-13.08.2009

-

Implmentierung und Evaluation aktueller Merkmalsextraktionsalgorithmen der bildbasierten ObjekterkennungStudent/in:Jahr: 2010Laufzeit: 11.06.2009-11.02.2010

-

Erweiterung der Ressourcen-Allokation bei Chipdesignprozessen auf multiple RessourcenStudent/in:Jahr: 2010Laufzeit: 03.05.2010-02.09.2010

-

Entwicklung einer Programmumgebung zur automatischen Generierung stückweise linearer BauelementmodelleStudent/in:Jahr: 2010Laufzeit: 03.11.2009-03.05.2010

-

VHDL-Implementierung des MFCC-Algorithmus zur AudiomerkmalsextraktionStudent/in:Jahr: 2010Laufzeit: 22.03.2010-30.09.2010

-

Konzeption und Implementierung einer Anwendung zur grafischen Darstellung von Bewegungsparametern auf SmartphonesStudent/in:Jahr: 2010Laufzeit: 06.05.2010-06.09.2010

-

Konzeptionierung und Implementierung eines Parallelisierungskonzepts zur Berechnung von dichten Disparitätsfeldern zur 3D-Rekonstruktion auf Graphics Processing UnitsStudent/in:Jahr: 2010Laufzeit: 05.05.2010-24.11.2010

![]()

![]()

-

Konzeption und Evaluation von Instruktionssatzerweiterungen zur Optical-Flow-Berechnung für einen ASIPStudent/in:Jahr: 2010Laufzeit: 31.05.2010-28.10.2010

-

Delphi/C++ Software-Entwicklung und Inbetriebnahme eines SAR-DemonstrationssystemsStudent/in:Jahr: 2011Laufzeit: 01.09.2011

-

Grafik-Coprozessoren zur parallelen AlgorithmenverarbeitungStudent/in:Jahr: 2011Laufzeit: 01.12.2010-01.04.2011

-

Vergleich eines exakten Verfahrens für das ressourcenbeschränkte Projekt-Scheduling-Problem mit einer heuristischen ImplementierungStudent/in:Jahr: 2011Laufzeit: 01.12.2010-31.05.2011

-

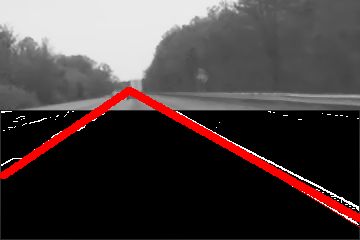

Konzeptionierung und Implementierung eines Low-Power-Protokollstacks für Wireless Sensor NetworksStudent/in:Jahr: 2011Laufzeit: 11.04.2011-27.10.2011

![]()

![]()

-

Evaluation von energieeffizienten, adaptiven und zuverlässigen Routingalgorithmen zum Einsatz in drahtlosen SensornetzwerkenMit Hilfe des Netzwerksimulators OMNeT++ sollen verschiedene Routingverfahren für drahtlose Netzwerke auf ihre energetischen Eigenschaften hin untersucht werden.Jahr: 2011Laufzeit: 15.06.2011-27.10.2011

![]()

![]()

-

Konzeption und Implementierung quantitativer Analysen zur Bewertung von Elastographie-DatenJahr: 2012Laufzeit: 02.01.2012-08.06.2012

-

Implementierung und Evaluierung von Befehlssatzerweiterungen zur Beschleunigung der Sound-Synthese auf einem Nios II ProzessorJahr: 2012Laufzeit: 03.05.2012-19.12.2012

-

Implementierung und Evaluierung eines Fixpunkt Kalman-Filters zur Sensordatenfusion von InertialsensorenJahr: 2012Laufzeit: 03.05.2012-12.10.2012

-

Entwicklung einer generischen Schnittstelle für Analogsimulatoren zur Simulationssprache SystemCJahr: 2012Laufzeit: 01.08.2008-21.03.2012

-

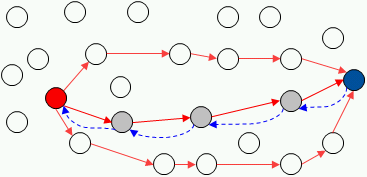

Konzeption und Implementierung eines Hardware-Moduls zur Echtzeit-Frequenz-Analyse von Audio-SignalenJahr: 2012Laufzeit: 20.12.2011-20.04.2012

-

Implementierung einer generischen Datenstruktur für die Umwandlung von NetzlistenformatenStudent/in:Jahr: 2012Laufzeit: 17.09.2012

-

Simulationsbasierte Evaluation der Eignung des ZigBee-Funkstandards zum Einsatz im Bereich der GebäudeautomatisierungMit Hilfe des Netzwerksimulators OMNeT++ soll simulativ analysiert werden, wie gut sich der Standard "ZigBee" zur Gebäudeautomatisierung eignet.Jahr: 2013Laufzeit: 23.05.2012-07.02.2013

![]()

![]()

-

Untersuchung und Verbesserung der Genauigkeit der Rechenoperationen in der Bibliothek für affine Arithmetik im AMV-SimulatorStudent/in:Jahr: 2013Laufzeit: 14.03.2013

-

Entwicklung von Inline-Profiling Methoden zur erweiterten Analyse des Laufzeitverhaltens paralleler FahrassistenzalgorithmenUm das nicht-deterministische Laufzeitverhalten von parallelen Programmen zu analysieren, werden bereits entwickelte Biblitoheksschnittstellen um Profiling-Methoden erweitert.Betreuung: Arndt, JakobStudent/in:Jahr: 2013Laufzeit: 09.12.2013-

![]()

![]()

-

Implementierung, Verifikation und Evaluation eines Mess-Moduls für medizinische SensorplattformenDiese Arbeit beschäftigt sich mit der Inbetriebnahme von chemischen Sensoren für die Überwachung von organischen Wachstumsvorgängen in Bioreaktoren. Der Fokus wird dabei vor allem auf die Temperatur und den pH-Wert gelegt.Student/in:Jahr: 2013Laufzeit: 20.12.2013-

![]()

![]()

-

Implementierung eines Ansatzes zur Berechnung der effektiven Kapazität für MehrfachtreibernetzeStudent/in:Jahr: 2014Laufzeit: 27.09.2007-01.04.2014

-

RAPANUI: Rapid Prototyping for Media Processor Architecture ExplorationBetreuung: Payá Vayá, GuillermoStudent/in:Jahr: 2014Laufzeit: 29.08.2005-01.04.2014

-

Werkzeug zur GlobalverdrahtungStudent/in:Jahr: 2014Laufzeit: 13.11.2007-01.04.2014

-

Entwicklung von Verdrahtungsstrategien zur ausfallsicheren VerdrahtungStudent/in:Jahr: 2014Laufzeit: 27.09.2007-01.04.2014

-

Optimierung und Implementierung einer modellbasierten Bewegungsschätzung für videobasierte FahrerassistenzsystemeBetreuung: Gregor Schewior, M.Sc.Jahr: 2014

-

Implementation of a Matlab Simulink Toolbox for Simulation and Evaluation of Dedicated Streaming-Architectures for Hearing Aid Signal Processing AlgorithmsBetreuung: Christopher SeifertJahr: 2014

-

Modellierung und Optimierung von Power/Ground Netzwerken im 3D-Floorplanning.Student/in:Jahr: 2014Laufzeit: 16.10.2012-01.04.2014

-

Aufbau, Integration und Programmierung einer PC-unabhängigen Steuereinheit zur Ansteuerung und Auswertung medizinischer SensorenIm Rahmen dieser Arbeit wurde ein ersten PC-unabhängiger Prototyp einer Steuereinheit für Bioreaktoren entwickelt.Student/in:Jahr: 2014Laufzeit: 11.01.2014-11.06.2014

![]()

![]()

-

Implementierung und Inbetriebnahme einer drahtlosen Inertial Measurement Unit unter Nutzung des Bluetooth Low Energy StandardsZur Bewegungserfassung sind sog. "Inertial Measurement Units" (IMUs) unerlässlich. Die Übertragung der erfassten Daten soll dabei drahtlos erfolgen. In dieser Arbeit soll daher eine IMU umgesetzt werden, welche Daten mittels des Übertragungsprotokolls "Bluetooth Low Energy" übermitteln kann.Student/in:Jahr: 2014Laufzeit: 01.04.2014-31.10.2014

![]()

![]()

-

Korrelationsanalyse von neuronalen AktivitätsmusternBetreuung: Payá Vayá, GuillermoStudent/in:Jahr: 2014Laufzeit: 27.05.2013-29.01.2014

![]()

![]()

-

Untersuchung der Möglichkeiten zur drahtlosen Informationsübertragung in BohrschlämmenZur Orientierung unter Tage werden zahlreiche Sensoren eingesetzt. Deren Daten müssen ausgewertet und an die Oberfläche weitergeleitet werden, um das eingesetzte Werkzeug entsprechend nachzuführen.Student/in:Jahr: 2014Laufzeit: 15.04.2014-

![]()

![]()

-

Entwicklung eines Verfahrens zur effizienten Modellgenerierung von stückweise linearen HDL-Modellen für eine beschleunigte Mixed-Signal-SimulationJahr: 2014Laufzeit: 02.07.2013-02.01.2014

-

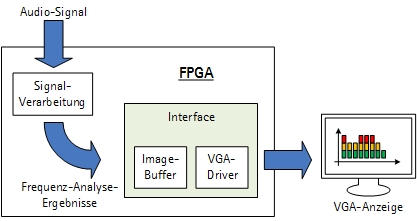

Konzeption und Implementierung eines Hardware-Interfaces zur Echtzeit-Visualisierung von Audio-Analyse-ErgebnissenZur Echtzeit-Visualisierung von Audio-Analyse-Ergebnissen über eine VGA-Anzeige soll eine komfortables Schnittstelle definiert und implementiert.Student/in:Jahr: 2014Laufzeit: 14.04.2014-

![]()

![]()

-

Konzeption und Implementierung einer Hardware-Einheit zur Frequenz-Analyse von Audio-Signalen zwecks Echtzeit-VisualisierungZur echtzeitfähigen Visualisierung soll ein Modul zur Frequenz-Analyse von Audio-Signalen konzipiert und implementiert werden.Student/in:Jahr: 2014Laufzeit: 14.03.2014-

![]()

![]()

-

Untersuchung und Implementierung eines dedizierten Hardware-Moduls zur interaktiven SoundsyntheseZur echtzeitfähigen Sonifikation von Bewegungen sollen VHDL-Module zur Soundsynthese entworfen und untersucht werden. Als Emulationsplattform wird hierfür das Digilent ZedBoard genutzt.Student/in:Jahr: 2014Laufzeit: 01.03.2014-

![]()

![]()

-

Implementierung und Evaluation einer Bewegungsschätzung für Fahrassistenzsysteme auf einem Multicore Mobil-Prozessor SoCZur Plattform-Evaluation eines Mobil-Prozessor SoCs mit Fahrassistenzalgorithmen soll eine Bewegungsschätzung implementiert werden, die die vorhandenen Hardware-Ressourcen möglichst gut ausnutzt.Betreuung: Arndt, JakobStudent/in:Jahr: 2014Laufzeit: 01.04.2014-

![]()

![]()

-

Implementierung eines MMSE-basierten Rauschreduktions-Algorithmus für Hörgeräte-SystemeAnhand einer Referenzimplementierung soll ein MMSE-basierter Rauschreduktionsalgorithmus in die IMS Matlab Hearing Aid Toolbox integriert, ein Vergleich mit vorhandenen Rauschreduktionsalgorithmen durchgeführt, eine Evaluation anhand verschiedener Filterbanken und eine Fixpunktimplementierung vorgenommen werden.Betreuung: Seifert, ChristopherStudent/in:Jahr: 2014Laufzeit: 20.12.2013-22.04.2014

-

Implementierung und Evaluierung von applikationsspezifischen Erweiterungen eines Soft-Core-Prozessors zur StereosignalverarbeitungDie Berechnung dichter Disparitätskarten soll auf einem Soft-Core ASIP implementiert werden. Anschließend sollen applikationsspezifische Anpassungen des Prozessors implementiert und evaluiert werden.Student/in:Jahr: 2014Laufzeit: 01.05.2014-31.08.2014

![]()

![]()

-

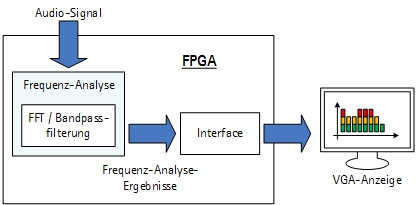

Implementierung einer Fahrspurerkennung auf einem applikationsspezifischen InstruktionssatzprozessorZur Evaluierung von anwendungsspezifischen Erweiterungen eines Soft-Core-Prozessors soll ein Algorithmus zur Fahrspurerkennung implemetiert werden.Student/in:Jahr: 2014Laufzeit: 20.05.2014-20.11.2014

![]()

![]()

-

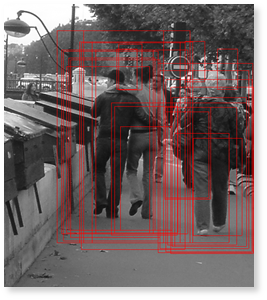

Implementierung und Evaluation von neuartigen Befehlssatzerweiterungen für Algorithmen zur FußgängererkennungFür die Erkennung von Fußgängern in Kamerabildern sollen anwendungsspezifische Erweiterungen eines Soft-Core-Prozessors implementiert und evaluiert werden.Student/in:Jahr: 2014Laufzeit: 20.05.2014-20.11.2014

![]()

![]()

-

Konzipierung und Implementierung von digitalen Sensorschnittstellen für eine Hochtemperatur-ASIC DemonstrationsplattformIm Rahmen bisheriger Forschungsaktivität zur Hochtemperaturelektronik in Bohrwerkzeugen wurde eine Prozessorarchitektur erarbeitet, welche die Bohrkopfnavigation bei geothermischen Bohrungen ermöglicht. Für die Überprüfung der Funktionalität dieser Architektur wird derzeit ein Demonstrationssystem aufgebaut, welches unter anderem die zu verarbeitenden Sensordaten an den Prozessor zuführt und die Berechnungen verifiziert. Für diesen Zweck sollen in dieser Arbeit zwei alternative Schnittstellen für das Demonstrationssystem implementiert und verifiziert werden.Student/in:Jahr: 2014Laufzeit: 05.05.2014-05.09.2014

![]()

![]()

-

Implementierung von Algorithmen zur Hardwarebeschleunigung in Software-Defined Radio SystemenBetreuung: Kock, MarkusStudent/in:Jahr: 2015Laufzeit: 04.08.2014-04.02.2015

-

Konzeptionierung und Implementierung von Mikrobenchmarks zur Analyse laufzeitentscheidender Charakteristika von MehrkernprozessorenZur Beurteilung relevanter Architekturentscheidungen von Mehrkernprozessoren werden in dieser Arbeit Mikrobenchmarks entwickelt, um Hardwareparameter von unterschiedlichen Prozessorklassen zu extrahieren.Betreuung: Arndt, JakobStudent/in:Jahr: 2015Laufzeit: 09.07.2014-09.01.2015

![]()

![]()

-

Hardware-Implementierung und Evaluierung eines merkmalsbasierten Optischen Flusses für FahrerassistenzsystemeZiel der Arbeit ist die VHDL-Implementierung eines Matching-Algorithmus auf Basis von FAST-BRIEF Merkmalen. Die gefundenen Merkmalskorrespondenzen können als dünn-besetztes optisches Flussfeld für weitere algorithmische Schritte verwendet werden.Betreuung: Hartig, JulianStudent/in:Jahr: 2015Laufzeit: 27.04.2015-11.11.2015

![]()

![]()

-

Evaluation von Pfadverlustmodellen für den Innenbereich sowie deren Eignung für gebäudespezifische DämpfungsvorhersagenDrahtloskommunikation innerhalb von Gebäuden wird maßgeblich von der Ausbreitung der Funksignale beeinflusst. Diese kann mit Hilfe von Pfadverlustmodellen abgeschätzt werden. Allerdings sind entsprechende Modelle für Vorhersagen im Innenbereich ungeeignet oder nicht exakt genug. Gegenstad der Arbeit ist es daher existente Modelle auf ihre Eignung hin zu untersuchen und Aussagen zur gebäudespezifischen Vorhersagbarket der Ausbreitung von Funksignalen zu treffen.Student/in:Jahr: 2015Laufzeit: 01.04.2015-01.10.2015

![]()

![]()

-

Evaluation der Leistungsfähigkeit eines VLIW-SIMD Signalprozessors für Speech-Enhancement-AlgorithmenEin Speech-Enhancement-Algorithmus soll in dieser Arbeit implementiert und evaluiert werden. Die zu evaluierende Prozessorarchitektur ist der am diesem Institut entwickelte VLIW-SIMD SignalprozessoBetreuung: Gerlach, LukasStudent/in:Jahr: 2015Laufzeit: 01.04.2015-

![]()

![]()

-

Implementierung und Evaluation eines Spracherkennungsalgorithmus auf einem VLIW-SIMD SignalprozessorEin Spracherkennungsalgorithmus soll in dieser Arbeit implementiert und evaluiert werden. Die zu evaluierende Prozessorarchitektur ist der am diesem Institut entwickelte VLIW-SIMD Signalprozessor.Betreuung: Gerlach, LukasStudent/in:Jahr: 2015Laufzeit: 01.04.2015-

![]()

![]()

-

Hardware Implementation and Evaluation of a Feature Extractor for Camera-based Driver Assistance SystemsIn this thesis, a FAST-BRIEF feature extractor shall be implemented for FPGA.Betreuung: Hartig, JulianStudent/in:Jahr: 2015Laufzeit: 06.10.2014-22.04.2015

![]()

![]()

-

Hardware-Implementierung und Evaluierung eines Merkmalextraktors für Kamera-basierte FahrerassistenzsystemeBetreuung: Hartig, JulianJahr: 2015

-

Konzeption, Implementierung und Verifikation eines Hardware-Moduls zur modellbasierten Bewegungsschätzung für videobasierte FahrerassistenzsystemeBetreuung: G. SchewiorJahr: 2015

-

Konzeptionierung und Implementierung einer parametrisierbaren Floating Point Unit für verschiedene FPGA-basierte ZielplattformenFür verschiedene Forschungsprojekte im Bereich der digitalen Signalverarbeitung wird im Rahmen dieser Arbeit ein dediziertes, parametrierbares Hardware-Modul für die Fließkommaberechnung auf FPGAs konzeptioniert und evaluiert.Betreuung: Spindeldreier, ChristianStudent/in:Jahr: 2015Laufzeit: 01.06.2015-18.12.2015

![]()

![]()

-

Hardwarenahe Datenübertragung über SPI mit DMA-Unterstützung für programmierbare LogikenIm Kontext der Automatisierungstechnik werden rekonfigurierbare Bussysteme eingesetzt, über welche die Kommunikation zwischen und innerhalb von Fertigungsmaschinen stattfindet. Auf Basis eines exemplarischen Controllers soll eine SPI-Datenübertragung mit DMA-Unterstützung realisiert werden.Betreuung: Wahalla, Marc-NilsStudent/in:Jahr: 2016Laufzeit: 06.07.2015-15.01.2016

![]()

![]()

-

Untersuchung von Fehlertoleranzmechanismen für FPGA-basierte Systeme zur LaserfrequenzbestimmungJahr: 2016

-

Implementierung und Modellierung exemplarischer Blöcke der Signalverarbeitung zur EntwurfsraumexplorationBetreuung: Julian Hartig, Dipl.-Ing.Student/in:Jahr: 2016

-

Implementierung und Evaluation eines bewegungskompensierten Deflickerverfahrens auf einer ASIP-ArchitekturBetreuung: Nicolai Behmann, M.Sc.Jahr: 2016

-

Konzeption, Implementierung und Evaluation eines Neuronalen Netzes zur Klassifikation von VerkehrszeichenBetreuung: Nicolai Behmann, M.Sc.Jahr: 2016

-

Implementierung und Evaluation eines Structure from Motion-Algorithmus zur 3D-Rekonstruktion aus monokularen VideoströmenBetreuung: Nicolai Behmann, M.Sc.Jahr: 2016

-

Implementierung und Modellierung exemplarischer Blöcke der Signalverarbeitung zur EntwurfsraumexplorationIn dieser Bachelorarbeit sollen 1D- und 2D-FIR Filter in VHDL flexibel implementiert und anschließend modelliert werden. Verschiedene Implementierungsalternativen sollen danach unter Verwendung eines kommerziellen Tools in einer Entwurfsraumexploration für unterschiedliche Randbedingungen einander gegenübergestellt und die Kosten verglichen werden.Betreuung: Hartig, JulianStudent/in:Jahr: 2016Laufzeit: 28.11.2016

![]()

![]()

-

Untersuchung von Fehlertoleranzmechanismen für FPGA basierte Systeme zur LaserfrequenzbestimmungIm Rahmen eines Forschungsprojekts werden Hardware Module für die Signalverarbeitung auf Weltraummissionen implementiert. Diese müssen auch unter den harten Weltraumbedingungen störungsfrei Funktionieren und insbesondere durch Single Event Effekts hervorgerufene Fehler kompensieren. Daher wird anhand der Fast-Fourier Transformation untersucht, mit welchen Mechanismen entsprechende Hardware-Module effizient geschützt werden kann.Betreuung: Spindeldreier, ChristianStudent/in:Jahr: 2016Laufzeit: 27.04.2016-23.11.2016

![]()

![]()

-

Untersuchung der Temperatur-Verlustleistungsbeziehung in FPGA-basierten SystemenAuf heutigen FPGAs sind analoge Temperatursensoren zur Überwachung der Die-Temperatur integriert. Da diese nur sehr wenige und lokal statisch sind, können durch spezielle Schaltungen (rückgekoppelte Inverterketten) auch digitale Temperatursensoren in LUTs oder DSPs abgebildet werden. In dieser Arbeit soll der Zusammenhang dieser digitalen Temperatur-Sensoren und der Verlustleistung eines FPGAs untersucht werden.Betreuung: Payá Vayá, Guillermo; Hartig, JulianStudent/in:Jahr: 2017Laufzeit: 27.10.2016-24.04.2017

![]()

![]()

-

Development of a Heating Appliance for the Characterization of High Temperature ASICsBetreuung: Webering, FritzJahr: 2017

-

Konzeption, Implementierung und Evaluation eines Stereomatching Algorithmus auf einer GPU für FahrerassistenzsystemeBetreuung: Behmann, NicolaiJahr: 2017

-

Analyse des Abtauschs zwischen Qualität und Rechenaufwand von Merkmalsdeskriptoren zur PunktkorrespondenzanalyseBetreuung: Hartig, JulianStudent/in:Jahr: 2017

-

Heterogene CPU/FPGA-Implementierung einer Disparitätsschätzung mit OpenCL High-Level Synthese und MPALBetreuung: Jakob ArndtJahr: 2017

-

Implementation and Evaluation of Time Domain Based Algorithms for the SAR Image Generation on a Mobile Processor SoCBetreuung: Matthis WielageStudent/in:Jahr: 2017

-

In-situ Untersuchung der Auswirkungen mechanischer Belastung mittels Nanoindentation auf elektronische BauelementeBetreuung: Christian SpindeldreierJahr: 2017

-

Konzeption eines Analog/Digital Interfaces für einen Distributed-Feedback-Laser und Integration in ein FPGA-basiertes SoC zur WellenlängenregelungFür Regelung der Laserfrequenz eines Distributed Feedback Lasers wird im Rahmen dieser Arbeit ein dediziertes Analog/Digital Interface für die FPGA-basierte Frequenzregelung mithilfe der Rubidium-Spektroskopie konzeptioniert und evaluiert.Betreuung: Spindeldreier, ChristianStudent/in:Jahr: 2017Laufzeit: 15.11.2016-09.06.2017

![]()

![]()

-

Konzeption und Implementierung eines FPGA-basierten Temperaturreglers für verstimmbare DiodenlaserFür die Erzeugung von Bose-Einstein-Kondensaten werden unter anderem verstimmbare Laser für eine optische Falle eingesetzt. Im Rahmen dieser Arbeit wird ein digitaler, FPGA-baiserter Temperaturregler entworfen, der die Laser auf einer vordefinierten Temperatur hält und an verschiedene Lasersysteme anpassbar ist.Betreuung: Spindeldreier, ChristianStudent/in:Jahr: 2017Laufzeit: 21.06.2017-19.12.2017

![]()

![]()

-

Konzeption, Implementierung und Evaluation einer Kompression von trainierten Modellen des Maschinellen LernensBetreuung: Nicolai Behmann, M.Sc.Jahr: 2018

-

Implementierung und Optimierung einer Fehlerkorrekturanwendung auf Basis einer Transport- Triggered-ProzessorarchitekturBetreuung: Moritz Weißbrich, M.Sc.Jahr: 2018

-

Design of a Scalable Application-Specific Architecture for Time-Domain Based SAR Imaging AutofocusBetreuung: Christian Fahnemann, M.Sc.Jahr: 2018

-

Optimierung und Parallelisierung eines Algorithmus zur Tiefenschätzung für eine massiv-parallele Vektor-ProzessorplattformBetreuung: Stephan Nolting, Dipl.-Ing.Jahr: 2018

-

Bildbasierte Detektion bewegter Bälle für die echtzeitfähige Anwendung in der SportanalyseBetreuung: Nicolai Behmann, M.Sc.Jahr: 2018

-

Conception, Implementation and Evaluation of an Application for assisted Labeling of Training Data for Machine LearningBetreuung: Nicolai Behmann, M.Sc.Jahr: 2018

-

Konzeptionierung, Implementierung und Evaluation eines Algorithmus zur Berechnung einer synthetischen Vogelperspektive für FahrerassistenzsystemeBetreuung: Nicolai Behmann, M.Sc.Jahr: 2018

-

Conception, Training and Evaluation of Algorithms for Classification of Medical DataBetreuung: Simon Klein, M.Sc.Jahr: 2018

-

Charakterisierung des Operationsverhaltens dedizierter FPGA-DSP-Blöcke unter stochastischen BetriebsbedingungenUm die Performance zur Echtzeitausführung von Computer-Vision-Anwendungen bei gleichzeitig geringem Energiebedarf bereitzustellen, werden applikationsspezifische Prozessoren und dedizierte Hardware-Blöcke eingesetzt. In dieser Arbeit soll das Fehlerverhalten der Multiplizierer in den dedizierten DSP-Blöcken eines FPGA-Bausteins untersucht und durch ein Fehlermodell charakterisiert werden, sobald stochastische Betriebsbedingungen durch Übertaktung vorliegen.Betreuung: Weißbrich, MoritzJahr: 2018

![]()

![]()

-

Optimierung und Parallelisierung eines Algorithmus zur Tiefenschätzung auf eine massiv parallele Vektor-ProzessorplattformAbbildung des SGM-Algorithmus zur Stereokamera-basierten Tiefenschätzung auf die VPRO SIMD-Vektor-Prozessorarchitektur.Betreuung: Nolting, Stephan; Payá Vayá, GuillermoStudent/in:Jahr: 2018Laufzeit: 19.10.2017-19.02.2018

![]()

![]()

-

Implementierung und vergleichende Evaluation von Deep Convolutional Neural Networks auf applikationsspezifischen HardwarearchitekturenIn einer Bachelor- oder Masterarbeit sollen unterschiedliche Architekturen tiefer Neuronaler Netze zur Klassifikation von Pixeln, Objekten oder Bildern aus der Literatur auf spezialisierte ASIPs, DSPs portiert oder FPGA-Implementierungen realisiert werden. In einer Simulation oder Emulation wird die Leistungsfähigkeit der Hardwareplattform evaluiert und ein Design-Space modelliert. Die Architektur des Neuronalen Netzes und Hardwareplattform wird in Abhängigkeit des Umfanges des Arbeit gemeinsam ausgewählt. Unter Umständen kann das Training der Neuronalen Netze hinsichtlich reduzierter Präzision und Komplexität ebenfalls betrachtet werden.Betreuung: Behmann, NicolaiJahr: 2018

![]()

![]()

-

Implementierung und Evaluierung von Algorithmen zur Optimierung von stückweise linearen BauelementmodellenIm Rahmen dieser Arbeit sollen verschiedene Methoden zur Optimierung von stückweise linearen Bauelementmodellen implementiert und anschließend evaluiert werden.Betreuung: Rechmal, MalgorzataJahr: 2018Laufzeit: 12.06.2018-

![]()

![]()

-

Implementierung und Evaluation von Augenerkennungs-Algorithmen für sportpraktische Testverfahren auf mobilen SystemenEs soll ein Verfahren entwickelt werden, das während der Durchführung verschiedener sportpraktischer Tests unter verschiedenen Umgebungsbedingungen feststellt, ob die Augen eines Probanden geöffnet oder geschlossen sind. Zunächst soll dabei ein kamerabasierter Ansatz verfolgt werden, der anhand von Kamerabildern des Probanden zuverlässig und schnell den Zustand der Augenlider erkennt.Betreuung: Webering, Fritz; Rother, NiklasStudent/in:Jahr: 2018Laufzeit: 06.06.2018-06.12.2018

-

Design of a scalable application-specific architecture for time-domain based SAR imaging autofocusDie Qualität der Bildgebung durch Radar mit synthetischer Apertur (SAR) sinkt durch Abweichungen von der idealen Flugbahn. Diese Abweichung muss zur Korrektur der Bildgebung sehr genau gemessen werden. Um den Restfehler weiter zu minimieren, können Autofokus-Verfahren eingesetzt werden. Ziel ist ein Architekturkonzept, um einen solchen Algorithmus in Hardware auszuführen.Betreuung: Fahnemann, ChristianStudent/in:Jahr: 2018Laufzeit: 19.06.2018-19.12.2018

![]()

![]()

-

Implementierung und Optimierung einer Fehlerkorrekturanwendung auf Basis einer Transport-Triggered-ProzessorarchitekturIn dieser Bachelorarbeit soll eine Fehlerkorrekturanwendung auf Basis des Reed-Solomon-Codes in C implementiert und für eine Transport-Triggered-Prozessorarchitektur (TTA) optimiert werden. Mithilfe des TTA-Based Co-Design Environments (TCE) der Universität Tampere, Finnland, werden dabei die Spezialisierung der Architektur vorgenommen und umfangreiche Analyse- und Profilingmöglichkeiten für die Optimierung der Anwendung und des applikationsspezifischen Prozessors bereitgestellt.Betreuung: Weißbrich, Moritz; Gesper, SvenStudent/in:Jahr: 2018

![]()

![]()

-

Implementierung eines Evaluationsframework zur Charakterisierung von FPGA synthetisiebaren echten ZufallszahlengeneratorenZahlreiche Anwendungen beruhen auf Zufallszahlen, die von den zugrunde liegenden Hardware-Plattformen generiert werden. Einfache (Pseudo-) Zufallsgeneratoren basieren auf iterativen Funktionen. Im Gegensatz dazu basieren echte Zufallszahlengeneratoren auf physikalischen Prozessen, die jenseits der Vorhersagbarkeit liegen. Daher können diese Architekturen zufällige Daten mit hoher Qualität liefern. In dieser Arbeit sollen mehrere FPGA synthetisierbare Zufallszahlengeneratoren implementiert und evaluiert werden.Betreuung: Nolting, StephanStudent/in:Jahr: 2018Laufzeit: 19.06.2018-18.12.2018

![]()

![]()

-

Erweiterung und Analyse von Verfahren zur Berücksichtigung von Eingangserregungen in Form von Rampenfunktionen für eine beschleunigte Mixed-Signal- SimulationBetreuung: Divanbeigi, SaraJahr: 2019

![]()

![]()

-

Konzeptionierung und Evaluierung von Strategien zur Parallelisierung eines beschleunigten Mixed-Signal-SimulatorsIm Rahmen dieser Arbeit sollen verschiedene Strategien der Parallelisierung des bislang sequentiellen PRAISE-Simulationskerns konzipiert und anschließend implementiert werden.Betreuung: Divanbeigi, SaraJahr: 2019

![]()

![]()

-

Implementierung einer GPU-beschleunigten Semantischen Segmentierung und Vergleich mit der parallelen CPU-Referenz-ImplementierungBetreuung: Jakob Arndt, Matthias LüdersJahr: 2019

-

Implementierung, Optimierung und Evaluierung eines massiv-parallelen Vektorprozessorsystems für die Xilinx ZYNQ UltraScale+ PlattformBetreuung: Stephan NoltingJahr: 2019

-

Implementierung und Evaluation eines Mikrocontroller-basierten Systems zur Erfassung von Sprunghöhen auf Basis druckabhängiger WiderständeBetreuung: Niklas RotherJahr: 2019

-

Entwurf, Implementierung und Evaluation eines Softwaresystems zur Aufzeichnung und Auswertung von SprungmessungenBetreuung: Niklas RotherJahr: 2019

-

Konzeption, Implementierung und Evaluation eines FPGA-basierten System on Chip für einen BUS-Controller für physikalische Experimente auf WeltraumplattformenBetreuung: Christian SpindeldreierJahr: 2019

-

Implementierung verschiedener DOA Algorithmen zur Abschätzung der Rechenleistung für eine parallele SignalverarbeitungBetreuung: Oliver RenkeJahr: 2019

-

Implementierung und Evaluation von Transformationsalgorithmen für ein hochauflösendes ScheinwerfersystemBetreuung: Jens SchleusnerJahr: 2019

-

Untersuchung und Bewertung von Komponenten für das kinetische Energy Harvesting in elektronischen SchließsystemenBetreuung: Moritz WeißbrichJahr: 2019

-

Implementation of an Evaluation Framework for Characterizing FPGA-Synthesizable True Random Number GeneratorsBetreuung: Stephan NoltingJahr: 2019

-

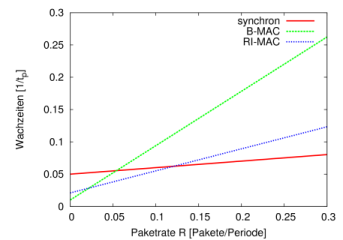

Dynamische Modellierung und Regelung eines vollintegrierten resonanten Switched-Capacitor-Spannungswandlers für Wearable-ApplikationenUm den fehlerfreien Betrieb eines Spannungswandlers zu gewährleisten, bedarf es einer stabilen und robusten Regelung. Bei der Auslegung der Regelung steht meist die Erfüllung der statischen Parameter, wie Eingangsspannungs- und Ausgangsleistungsbereich im Fokus. Für die Auslegung des Wandlers ist unter anderem eine möglichst genaue Beschreibung des Wandlers für den statischen Betriebspunkt erforderlich. Die Modellierung und Regelung eines geeigneten Switched-Capacitor-Spannungswandlers ist die Herausforderung in dieser Arbeit. Die Arbeit wurde ausgezeichnet mit dem VDE-Preis 2020!Betreuung: Peter RenzStudent/in:Jahr: 2019Laufzeit: 16.3.2010-16.9.2019

![]()

![]()

-

Konzeption, Training und Evaluation approximativer Neuronaler Netze zur ObjekterkennungBetreuung: Nicolai Behmann, M.Sc.Jahr: 2020

-

Low Power Design Methodologies for ASIP-Based Hearing Aid Systems using a 22nm FD-SOI TechnologyBetreuung: Jens Karrenbauer, M.Sc.Jahr: 2020

-

Evaluierung und Optimierung einer ASIP-Architektur für einen Rauschunterdrückungsalgorithmus für Digitale HörhilfenBetreuung: Jens Karrenbauer, M.Sc.Jahr: 2020

-

Implementation of a Software Framework for Instruction-Set Encoding Optimization of Embedded Processors using Evolutionary AlgorithmsBetreuung: Moritz Weißbrich, M.Sc.Jahr: 2020

-

Implementierung und Evaluation eines kamerabasierten Systems zur SprunghöhenmessungBetreuung: Fritz Webering, M.Sc.Jahr: 2020

-

Design and Implementation of a Battery Management System and a Power Electronic Circuit for Photovoltaic Power Supply of NanosatellitesBetreuung: Adrian GehlStudent/in:Jahr: 2020Laufzeit: 15.11.2019-15.05.2020

-

Implementierung eines Maximum-Power-Point-Tracking-Algorithmus und einer Steuerungssoftware für ein photovoltaisches Energieversorgungssystem für NanosatellitenBetreuung: Adrian GehlStudent/in:Jahr: 2020Laufzeit: 15.11.2019 - 15.05.2020

-

Entwurf und Simulation eines mehrphasigen Abwärtswandlers zur Untersuchung der Vorteile mehrphasiger WandlertopologienMehrphasige Abwärtswandler sind ein vielversprechender Ansatz, um die benötigten passiven Bauelemente induktiver Wandler zu verkleinern. Ziel dieser Arbeit ist die Analyse des Einfluss von Parametern wie der Anzahl der Phasen, Betriebsmodus des Wandlers (CCM, BCM, DCM) und verwendetem Regelverfahren (constant on/off time, hysteretic control, u.a.) auf den Verlauf des Ausgangsstroms und den Wirkungsgrad eines mehrphasigen Abwärtswandlers und diese Ergebnisse mit dem Verhalten eines einphasigen Wandlers zu vergleichen.Betreuung: Ferdinand PieperStudent/in:Jahr: 2020Laufzeit: 1.5.2020-1.11.2020

![]()

![]()

-

Verbesserung eines kamerabasierten Systems zur Sprunghöhenmessung mithilfe von neuronalen NetzenBetreuung: Fritz WeberingJahr: 2021

-

Implementierung und Evaluation von Algorithmen zur 3D-Oberflächenmessung Nicht-Statischer Objekte mit Structured LightBetreuung: Henrik HeymannJahr: 2021

-

Implementierung einer modularisierten Software-Pipeline zur Anonymisierung von VideosequenzenBetreuung: Julian DrewljauJahr: 2021

-

Implementierung und Evaluation eines Open-Source Beschleunigers für Neuronale Netze auf FPGAsBetreuung: Julian DrewljauJahr: 2021

-

Realisierung einer Gate-Treiber-Versorgung mit Fly-back-Prinzip für die Ansteuerung moderner LeistungstransistorenIn dieser Arbeit wird die Kombination aus einem Abwärtswandler zusammen mit einer gekoppelten Spule verwendet, um eine sekundäre Ausgangsspannung zu erzeugen. Mit dieser sekundären Spannung kann wiederum die Versorgung der Gatetreiber sichergestellt werden, um die Schaltung effizient bei hohen Eingangsspannungen zu versorgen. Um hohe Eingangsspannungen effizient zu unterstützen, werden GaN-Leistungstransistoren verwendet. Die Schaltung wird auf einer diskreten Testplatine aufgebaut.Betreuung: Christoph HillmerStudent/in:Jahr: 2021Laufzeit: 23.11.2020-22.05.2021

![]()

![]()

-

Erweiterung und Optimierung eines Compilers für einen Application Specific Instruction Set Processor mithilfe von LLVMBetreuung: StuckmannJahr: 2021

-

Analyse, Implementierung und Evaluation von Verfahren zur automatisierten Ereignisdetektion in Videoaufzeichnungen zur Generierung von Markern in EEG-DatensätzenBetreuung: Simon Klein, Marc-Nils WahallaJahr: 2021

-

Benchmarking and Comparison of a TriCore AURIX Platform for Realization of AI AlgorithmsBetreuung: Christoph RiggersJahr: 2021

-

Implementierung und Evaluation einer automatischen Laufzeitberechnung für simultane Auslöser in polymerfaserbasierten Netzwerken für die Kommunikation bei WeltraumanwendungenBetreuung: Tim OberschulteJahr: 2021

-

Entwurf und Implementierung einstellbarer Delays als Teil einer adaptiven Totzeitregelung in einer 55-nm-TechnologieZiel dieser Arbeit ist der Entwurf eines adaptiven Delays, das zum Einstellen von Totzeiten in einer Zero-Voltage-Switching-(ZVS)-Regelung eingesetzt werden kann. Um die Funktionsfähigkeit des ZVS für verschiedene Anwendungsfälle zu gewährleisten, muss dabei ein besonders großer Stellbereich der Delays erreicht werden.Betreuung: Ferdinand PieperStudent/in:Jahr: 2021Laufzeit: 1.4.2021-1.10.2021

-

Konzeption, Training und Evaluation eines Neuronalen Netzes für Demosaicking und Rauschreduktion von BildsensorrohdatenBetreuung: Nicolai Behmann, Julian DrewljauJahr: 2021

-

Entwurf, Implementierung und Evaluation eines Radar-Simulators für komplexe SzenenBetreuung: Niklas RotherJahr: 2021

-

Implementierung und Evaluation eines HD-Scheinwerfersystems zur Projektion der FahrzeugtrajektorieBetreuung: Jens SchleusnerJahr: 2021

-

Implementation and Evaluation of a Real Time Firmware for Inertial Measurement Units with Bluetooth Low EnergyBetreuung: Fritz WeberingJahr: 2021

-

Hardwareoptimierte Segmentierung auf Basis von LiDAR- und BilddatenBetreuung: Günther Meyer, M.Sc.Jahr: 2022

-

Performance Analysis for Convolutional Neural Networks on Hardware AcceleratorsBetreuung: Günther Meyer, M.Sc.Jahr: 2022

-

Implementierung und Optimierung eines Algorithmus zur Punktwolkenprojektion auf einer RISC-V-ArchitekturBetreuung: Oliver Renke, M.Sc.Jahr: 2022

-

Simulationsbasierte Evaluation von Hardwarebeschleunigern anhand von verschiedenen Audio-ApplikationenBetreuung: Jens Karrenbauer, M.Sc.Jahr: 2022

-

Evaluation und Optimierung einer Transport Triggered Architecture für den Einsatz von Synthetic-Aperture-Radar-AlgorithmenBetreuung: Niklas Rother, M.Sc.Student/in:Jahr: 2023

-

Messung und Untersuchung des Induktanzabfalls bei integrierten Spulen unter verschiedenen DC- und AC-Testbedingungen.Im Rahmen dieser Arbeit wurde die Bedeutung integrierter Spulen für hochkompakte DC-DC Wandler untersucht. Dabei wurde der Einfluss von hohen Frequenzen auf die Reduktion von Größe, Gewicht und Kosten von Spulen betrachtet und die Sättigungseffekte, die deren Leistungsabgabe limitieren, analysiert. Es wurden Messungen zur "Induktivitätsabnahme" bei steigenden Strömen durchgeführt, die Induktivitäts-Strom-Diagramme dokumentiert und ein Bias-Tee mit hoher Stromkapazität gebaut, um den Einfluss von AC- und DC-Strömen auf das Verhalten der Spulen zu verstehen; die Verbindung zwischen Spulengeometrie und Designparametern wurde ebenfalls untersucht.Betreuung: Ferdinand PieperStudent/in:Jahr: 2023Laufzeit: 17.10.2022 – 17.04.2023

![]()

![]()

-

Entwurf und Charakterisierung von passiven dreidimensionalen Komponenten auf additiv gefertigten LeiterplattenIm Rahmen dieser Arbeit wurden Spulen und Kondensatoren verschiedener Bauformen entworfen und mittels additiver Fertigung hergestellt. Ziel war es, das Potenzial der additiven Fertigung für in Leiterplatten integrierte passive Bauelemente zu bewerten und deren Eignung als Kompromisslösung zwischen vollständig integrierten und diskreten Bauelementen abzuschätzen.Betreuung: Ferdinand PieperStudent/in:Jahr: 2023Laufzeit: 15.12.2022 – 15.06.2023

![]()

![]()

-

Implementation and Evaluation of Reference Systems for Computed Order Tracking AlgorithmsBetreuung: Jens Karrenbauer, M.Sc.Jahr: 2023

-

Untersuchung von Memristoren für die Anwendung in neuronalen NetzenKünstliche neuronale Netze (KNN) gewinnen durch die Fortschritte in der künstlichen Intelligenz zunehmend an Bedeutung, da sie komplexe Muster analysieren und in analoger Form energieeffizienter arbeiten als herkömmliche Computerarchitekturen. Ähnlich wie natürliche neuronale Netze bestehen sie aus Neuronen, die Signale verarbeiten, und Synapsen, die Verbindungen gewichten. Diese Gewichtung erfolgt durch Anpassung der Verbindungseigenschaften, um Lernprozesse zu ermöglichen. Eine vielversprechende Methode zur Realisierung künstlicher Synapsen ist der Einsatz von Memristoren. Diese Bauelemente ermöglichen eine effiziente und anpassungsfähige Gewichtung der Verbindungen in KNN.Betreuung: Saurabh KaleStudent/in:Jahr: 2023Laufzeit: 04.04.2023 - 04.10.2023

-

Untersuchung von piezoelektrischen Resonatoren und Entwicklung einer Messschaltung.Dieses Projekt untersucht die Verwendung von piezoelektrischen Resonatoren (PRs) als Alternative zu Induktivitäten und Kapazitäten zur Energiespeicherung in Stromversorgungsanwendungen. Im Gegensatz zu sperrigen Induktivitäten bieten PRs eine höhere Energiedichte, effiziente Leistungsumwandlung und eine bessere Integration in ICs aufgrund ihrer planaren Geometrie. Sie minimieren zudem elektromagnetische Störungen und vermeiden Wicklungsverluste bei hohen Frequenzen. Eine Leiterplatte wurde entworfen, um die Anwendung von PRs in einem Buck-Boost-DC-DC-Wandler zu testen. Die Studie bewertet verschiedene PR-Konfigurationen hinsichtlich ihrer Effektivität in Energiemanagementsystemen.Betreuung: Saurabh KaleStudent/in:Jahr: 2023Laufzeit: 30.10.2022 - 30.04.2023

-

Adaptive Regelung von DC-DC-Konvertern unter Einsatz von Machine-Learning-AlgorithmenBetreuung: Dr.-Ing. Markus OlbrichStudent/in:Jahr: 2023Laufzeit: 24.7.2023-24.11.2023

-

Implementierung und Evaluierung eines Algorithmus zur Lokalisierung von Geräuschquellen auf einem ASIP für digitale HörhilfenBetreuung: Sven Schönewald, Jens KarrenbauerJahr: 2023

-

Evaluation und Implementierung verschiedener Kanalkodierungen zur Durchsatzoptimierung fehleranfälliger KanäleBetreuung: Till FiedlerJahr: 2023

-

Implementierung und Optimierung eines Algorithmus zur Geräuschunterdrückung auf einem ASIP basierten Hardwaredemonstrator für digitale HörhilfenBetreuung: Sven ShcönewaldJahr: 2023

-

Topologische Optimierung des neuronalen Netzes SalsaNext für die effiziente Ausführung auf einer VektorprozessorarchitekturBetreuung: Oliver RenkeJahr: 2023

-

Evaluation und Optimierung einer Transport Triggered Architecture für den Einsatz von Synthetic-Aperture-Radar-AlgorithmenBetreuung: Niklas RotherJahr: 2023

-

Skalierbarkeit von Datenkompression für Neuronale NetzeBetreuung: Simon KleinJahr: 2023

-

Implementierung eines Moduls zur Zerlegung von CNN-Operationen in parallelisierbare Workloads und Integration in Apache TVM CNN-CompilerBetreuung: Oliver RenkeJahr: 2023

-

Entwicklung einer Compiler-Toolchain für einen Hochperformanten RISC-V ProzessorBetreuung: Malte HawichJahr: 2023

-

Entwurf und Integration von Hardware Schedulern einer n-stufigen Pipeline für einen RISC-V Prozessor in einer HochtemperaturumgebungBetreuung: Malte HawichJahr: 2023

-

Implementierung eines Moduls zur Quantisierung von CNN-Operationen und Integration in Apache TVM CNN-CompilerBetreuung: Oliver RenkeJahr: 2023

-

Modellierung der Induktorkopplung in mehrphasigen DC-DC WandlernIm Rahmen dieser Arbeit wurde der Einfluss gekoppelter Induktivitäten in mehrphasigen DC-DC Wandlern untersucht. Basierend auf einer Zustandsraumdarstellung wurde ein Simulationsmodell entwickelt, um das Verhalten verschiedener Kopplungsfaktoren im gleichen System zu vergleichen, wobei insbesondere Effekte auf den Stromrippel jeder Phase, den durchschnittlichen Strom, die Reaktion auf Lastsprünge und die Stabilität analysiert wurden. Das Modell soll den Designprozess unterstützen, indem es die Auswirkungen unterschiedlicher Kopplungen visualisiert und so die Auslegung geeigneter mehrphasiger Wandler mit gekoppelten Induktivitäten beschleunigt.Betreuung: Ferdinand PieperStudent/in:Jahr: 2024Laufzeit: 15.08.2023 – 15.02.2024

-

Untersuchung von SpannungswandlerkombinationenIm Rahmen dieser Bachelorarbeit wurden Spannungswandler untersucht, die eine Kombination aus Switched-Capacitor- und Buck-Wandlerstufen darstellen. Der Schwerpunkt lag auf der Analyse des Soft-Charging-Verhaltens der kombinierten Stufen und dessen Einfluss auf die Reduktion von Verlusten, die Steigerung der Leistungsdichte sowie die Verbesserung der Effizienz. Zur Validierung der Simulationsergebnisse wurde ein diskreter Demonstrator entwickelt.Betreuung: Tim KuhlmannStudent/in:Jahr: 2024Laufzeit: 2.6.2024-2.12.2024

![]()

![]()

-

Gate Driving Techniques for Hybird 48V DC-DC ConvertersModerne Recheneinheiten in Data Centers benötigen hocheffiziente 48V:1V DCDC Wandler mit hoher Leistungsdichte. Hybride Switched-Capacitor DCDC Wandler stellen eine Klasse von vielversprechenden Topologien dar. Ziel der studentischen Arbeit ist die Erarbeitung von geeigneten Gate-Treiber-Konzepten für hybride Switched-Capacitor DCDC Wandler in 48V Anwendungen. Ein besonderer Fokus liegt hierbei auf der Erzeugung der Gate-Treiber-Versorgung von Schaltern mit fliegenden Source Potentialen, welche in dieser Topologieklasse häufig vorkommen.Betreuung: Joseph WinklerStudent/in:Jahr: 2024Laufzeit: 18.10.2024 - 18.04.2025

-

Entwurf eines Hochspannungsmesssystems zur Charakterisierung von Derating-Effekten bei MLCCs.Zur Untersuchung der Derating-Effekte von Keramikkondensatoren (MLCCs) soll ein Messsystem entwickelt werden, das Testsignale mit variabler Bias-Spannung und unterschiedlichen Signalfrequenzen erzeugen kann. Zusätzlich soll es ermöglichen, die effektive Gesamtkapazität unter diesen Betriebsbedingungen präzise zu bestimmen. Der Fokus liegt auf DC-Spannungen bis 200 V. Mithilfe des Systems sollen zudem exemplarisch Derating-Effekte analysiert und bewertet werden.Betreuung: Tim KuhlmannStudent/in:Jahr: 2025Laufzeit: 19.03.2025 - 19.09.2025

Master-/Diplomarbeit

-

Implementierung und Evaluierung einer FPGA-basierten ASIP-Architektur für die Extraktion von FAST-BRIEF-BildmerkmalenZur beschleunigten Extraktion von FAST-BRIEF-Bildmerkmalen soll der Instruktionssatz eines ASIPs erweitert werden. In dieser Arbeit wird evaluiert, in welchem Verhältnis der durch die Erweiterung entstehende zusätzliche FPGA-Ressourcenbedarf zu dem erzielten Geschwindigkeitsgewinn bei der Bildmerkmalsextraktion steht.Student/in:

![]()

![]()

-

Konzeptionierung und Implementierung einer FPGA-basierten Architektur für das Finden korrespondierender Bildmerkmale in StereobildpaarenZum Finden korrespondierender SIFT-Bildmerkmalen in Stereobildpaaren können verschiedene Matching-Algorithmen Anwendung finden. In dieser Arbeit ist ein für diese Applikation passender Matching-Algorithmus zu identifizieren und diesen auf einer FPGA-basierten Architektur zu implementieren.Student/in:

![]()

![]()

-

Entwicklung, Integration und Evaluation einer elektro-chemischen Biosensor-Einheit für BioreaktorenDies Arbeit beschäftigt sich mit dem Aufbau einer spezialisierten Messeinheit auf Basis von elektro-chemischen Sensoren. Mit dieser Messeinheit sollen organische Wachstumsvorgänge in medizinischen Bioreaktoren überwacht werden.Student/in:

![]()

![]()

-

Evaluierung approximierender arithmetischer Einheiten für Stochastic-Computing-Anwendungen in horizontalen und vertikalen SIMD-VektorprozessorenEine Möglichkeit zur Reduzierung der Leistungsaufnahme von Prozessoren besteht in der Verringerung der Versorgungsspannung, wodurch jedoch Timing-Verletzungen und fehlerhafte Ergebnisse berücksichtigt werden müssen (Stochastic-Computing-Ansatz). Der Abtausch zwischen stochastischer Rechenungenauigkeit und Verlustleistung/Performance soll dabei im Rahmen dieser Arbeit anhand applikationsspezifischer horizontaler und vertikaler SIMD-Vektorprozessoren evaluiert und quantifiziert werden.Betreuung: Weißbrich, MoritzStudent/in:

![]()

![]()

-

Implementierung und Evaluierung von Computer-Vision-Algorithmen zur Merkmalsextraktion auf horizontalen und vertikalen SIMD-VektorprozessorenDie Echtzeitausführung rechenintensiver Computer-Vision-Algorithmen erfordert eine hohe Leistungsfähigkeit/Performance der Architektur bei einem stark beschränkten Verlustleistungsbudget. Daher werden applikationsspezifische Vektorprozessoren eingesetzt, um eine in Bezug auf Performance-pro-Watt optimierte Verarbeitung zu erreichen. Im Rahmen dieser Arbeit sollen Computer-Vision-Algorithmen zur Merkmalsextraktion für die genannten Vektor-Prozessorarchitekturen unter Ausnutzung der architekturspezifischen Datenparallelität implementiert werden. Weiterhin ist die Evaluation von Performance und Verlustleistung bei Ausführung der implementierten Applikationen Bestandteil der Arbeit.Betreuung: Weißbrich, MoritzStudent/in:

![]()

![]()

-

Implementierung eines VLIW-MIPS-Prozessors für Hochtemperaturanwendungen mit CompilerunterstützungIn dieser Arbeit soll eine VLIW-Variante eines am Institut vorhandenen MIPS-Prozessors durch Hinzufügen eines zweiten Issue Slots entwickelt und implementiert werden. Damit die im Laufe dieser Arbeit entwickelte Architektur in C/C++ programmiert werden kann, ist eine entsprechende Compilerunterstützung bereitzustellen. Dafür soll das bestehende MIPS-Backend des Open Source Compilers LLVM angepasst und erweitert werden.Betreuung: Nolting, StephanStudent/in:

![]()

![]()

-

Implementierung eines FPGA-basierten Systems zur Charakterisierung von SpeicherbausteinenAufbau eines FPGA-basierten Soft-Core-Prozessorsystems zur automatischen Charkterisierung von elektronischen SpeichermodulenBetreuung: Nolting, Stephan; Payá Vayá, GuillermoStudent/in:

![]()

![]()

-

Implementierung und Evaluierung generischer Addierer- und Multipliziererarchitekturen für Approximate-Computing-AnwendungenIn der Literatur werden verschiedene approximative Architekturmodifikationen für Addierer und Multiplizierer präsentiert, wobei jede Architektur eine eigene Charakteristik bzgl. des Approximationsfehlers, benötigter Chipfläche und Verlustleistung sowie möglicher Performance aufweist. Eine vollständige Evaluation der vorgeschlagenen Approximationsansätze ist daher unumgänglich für die Auswahl geeigneter, auf eine Applikationsklasse spezialisierter arithmetischer Hardware. In dieser Arbeit soll eine Auswahl approximierender Addierer- und Multipliziererarchitekturen aus der Literatur als strukturelle und generische RTL-Beschreibung in der Hardware-Beschreibungssprache VHDL implementiert werden.Betreuung: Weißbrich, Moritz

![]()

![]()

-

Implementierung und Optimierung eines MIPS-basierten Soft-Core-Prozessorsystems zur VerkehrszeichenerkennungBesonders im Automobilbereich und im Kontext der Fahrerassistenzsysteme werden Architekturen für komplexe Berechnungen eingesetzt, die unter harten Echtzeitanforderungen arbeiten müssen. Besonders die Entwicklung von sogenannten Soft-Core-Prozessoren für den Einsatz in Field Programmable Gate Arrays (FPGAs) ist Gegenstand aktueller Forschungen. Durch dedizierte Erweiterungen einer Basisarchitektur kann der Prozessor für eine bestimmte Anwendung oder ein Aufgabengebiet optimiert werden. Spätere Anpassungen der Architektur sind durch die Rekonfigurierbarkeit des FPGAs weiterhin gegeben, sodass derartige Prozessor-plattformen einen guten Abtausch zwischen Kosten, Rechenleistung und Effizienz bieten.Betreuung: Nolting, StephanStudent/in:

-

Implementierung und Optimierung eines MIPS-basierten Soft-Core-Prozessorsystems für ein Xilinx Arty-FPGA-BoardDie Aufgabe in dieser Arbeit besteht darin, einen zuvor entworfenen MIPS Soft-Core-Prozessor für eine kostengünstige Xilinx Arty FPGA-Platine zu implementieren und zu optimieren.Betreuung: Nolting, Stephan; Hartig, JulianStudent/in:

-

Implementierung und Evaluierung eines Frameworks zur Charakterisierung kommerzieller FPGAsBasierend auf früheren Arbeiten ist die Aufgabenstellung dieser Arbeit, mehrere Xilinx Virtex-6 FPGAs auf ihre maximale physikalische Betriebsfrequenz zu charakterisieren. Die minimale Laufzeitverzögerung soll mit Oszillatoren analysiert werden, die mit den rekonfigurierbaren FPGA-Basiselementen aufgebaut werden.Betreuung: Nolting, Stephan

-

Implementierung und Evaluierung von eng gekoppelten SIMD- und Vektor-Koprozessoren mit einem MIPS ProzessorDie Aufgabe in dieser Arbeit ist es, einen vertikalen und einen horizontalen Vektor-Coprozessor für eine am Institut für Mikroelektronische Systeme entwickelte MIPS-basierte Architektur zu entwerfen und zu implementieren.Betreuung: Nolting, Stephan

-

Implementierung und Evaluierung eines CNN-basierten Szenenkennzeichnungsalgorithmus auf einer neuartigen komplexadressierenden Vektor-Co-Prozessor-ArchitekturDie Aufgabe dieser Arbeit besteht darin, den Open-Source-LLVM-Compiler so zu modifizieren, um eine neuartige komplexe Vektor-Coprozessorarchitektur zu unterstützen.Betreuung: Nolting, Stephan

![]()

![]()

-

Konzeption und Implementierung einer Hardware/Software-Schnittstelle zur parallelen Taskverarbeitung auf einer modularen CoprozessorarchitekturStudent/in:Jahr: 2009Laufzeit: 07.07.2008-16.01.2009

-

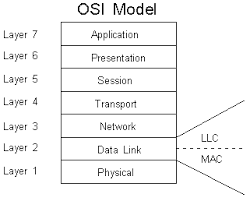

Analyse der Hardware-Anforderungen für die Verarbeitung der höheren Protokollschichten in aktuellen Interconnect-TechnologienStudent/in:Jahr: 2009Laufzeit: 15.10.2008-12.06.2009

-

Untersuchung von Sampling-Verfahren zur statistischen Modellierung von digitalen StandardzellenStudent/in:Jahr: 2009Laufzeit: 25.11.2008-02.06.2009

-

Entwurf eines MOSFET-Modells unter Verwendung affiner ArithmetikStudent/in:Jahr: 2010Laufzeit: 01.04.2010

-