Zeige Ergebnisse 1 -

6

von 6

2024

A Reconfiguration Strategy for Distributed Electronic Systems on ISS. /

Oberschulte, Tim; Marten, Jakob Frederik; Wendrich, Thijs Jan et al.

2024. Postersitzung präsentiert bei 28th ELGRA Biennial Symposium & General Assembly, Liverpool, Großbritannien / Vereinigtes Königreich.

Publikation: Konferenzbeitrag › Poster › Forschung › Peer-Review

An Affordable Autonomous 2U-Greenhouse for Plant Research in low-gravity Environments. /

Woiwode, Dominik; Marten, Jakob Frederik; Behrens, Dörthe et al.

2024. Postersitzung präsentiert bei 28th ELGRA Biennial Symposium & General Assembly, Liverpool, Großbritannien / Vereinigtes Königreich.

Publikation: Konferenzbeitrag › Poster › Forschung › Peer-Review

2023

Fault Detection Mechanisms for COTS FPGA Systems Used in Low Earth Orbit. /

Oberschulte, Tim; Marten, Jakob; Blume, Holger.

Embedded Computer Systems: Architectures, Modeling, and Simulation - 23rd International Conference, SAMOS 2023, Proceedings. Hrsg. / Cristina Silvano; Marc Reichenbach; Christian Pilato. Springer International Publishing AG, 2023. S. 19-32 (Lecture Notes in Computer Science (including subseries Lecture Notes in Artificial Intelligence and Lecture Notes in Bioinformatics); Band 14385 LNCS).

Publikation: Beitrag in Buch/Bericht/Sammelwerk/Konferenzband › Aufsatz in Konferenzband › Forschung › Peer-Review

Fault Detection on Multi COTS FPGA Systems for Physics Experiments on the International Space Station. /

Oberschulte, Tim; Marten, Jakob; Blume, Holger.

FPGA '23: Proceedings of the 2023 ACM/SIGDA International Symposium on Field Programmable Gate Arrays. Association for Computing Machinery (ACM), 2023.

Publikation: Beitrag in Buch/Bericht/Sammelwerk/Konferenzband › Sonstiger Beitrag in Buch/Bericht/Sammelwerk oder Konferenzband › Forschung › Peer-Review

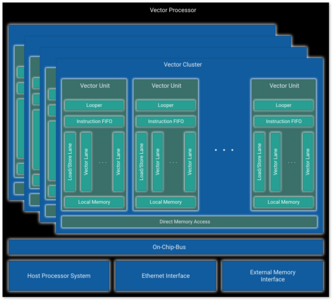

ZuSE KI-AVF: Application-Specific AI Processor for Intelligent Sensor Signal Processing in Autonomous Driving. /

Thieu, Gia Bao; Gesper, Sven; Payá-Vayá, Guillermo et al.

2023 Design, Automation and Test in Europe Conference and Exhibition, DATE 2023 - Proceedings. IEEE, 2023. (Design, automation and test in Europe conference).

Publikation: Beitrag in Buch/Bericht/Sammelwerk/Konferenzband › Aufsatz in Konferenzband › Forschung › Peer-Review

Pflanzenforschung an Bord der ISS: Wettbewerb "Überflieger 2". / Wörz, Nils; Sondheim, Justin; Behrens, Dörthe et al.

in:

BioSpektrum, Jahrgang 29, Nr. 5, 09.2023, S. 557.

Publikation: Beitrag in Fachzeitschrift › Übersichtsarbeit › Forschung › Peer-Review