Smart Hearing Aid Processor (Smart HeaP)

| Leitung: | Prof. Dr.-Ing. H. Blume |

| Team: | M.Sc. J. Karrenbauer, M.Sc. S. Klein, M.Sc. S. Schönewald |

| Jahr: | 2018 |

| Datum: | 06-05-18 |

| Förderung: | BMBF |

| Laufzeit: | April 2018 - Juni 2022 |

| Ist abgeschlossen: | ja |

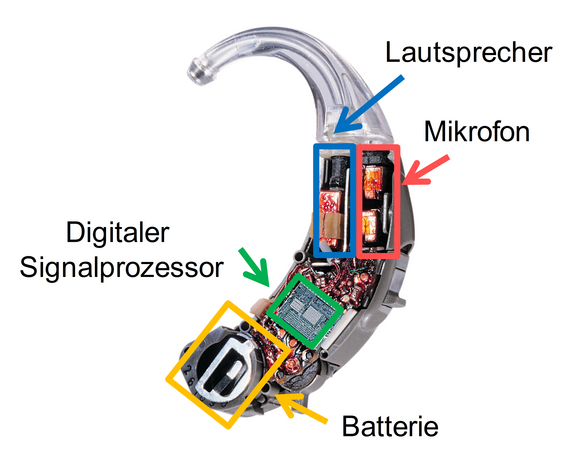

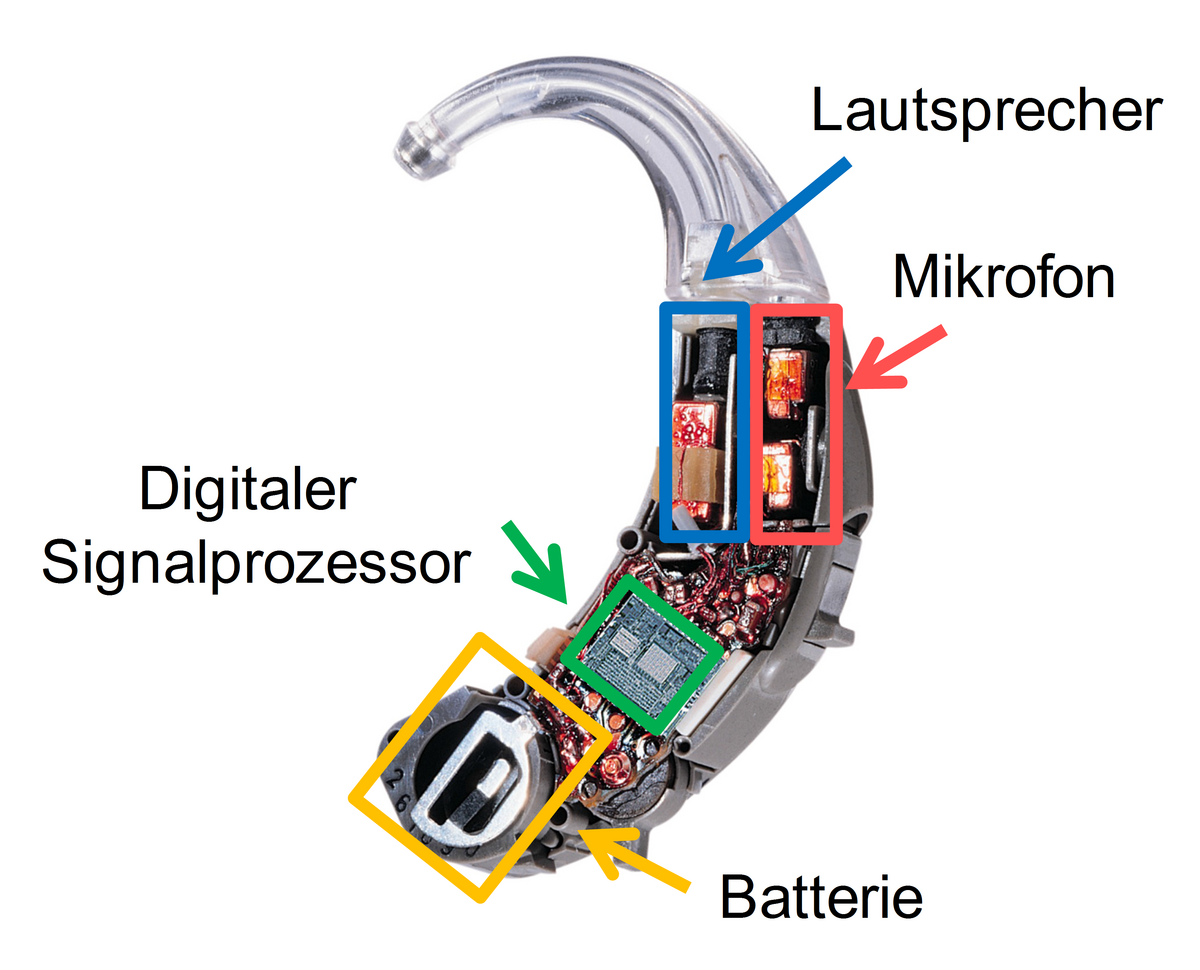

Der Nutzen und die Akzeptanz von Hörhilfen kann nur gewährleistet werden, wenn die komplexen technischen Randbedingungen eingehalten werden. Zu diesen Randbedingungen gehören miniaturisierte Bauformen, sehr kurze Latenzen bei der Audio-Signalverarbeitung und insbesondere ein extrem limitiertes Verlustleistungs-Budget, um lange Batterielaufzeiten zu erzielen.

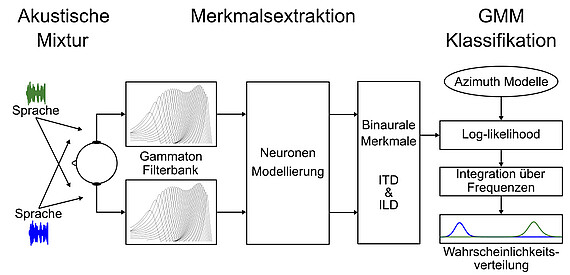

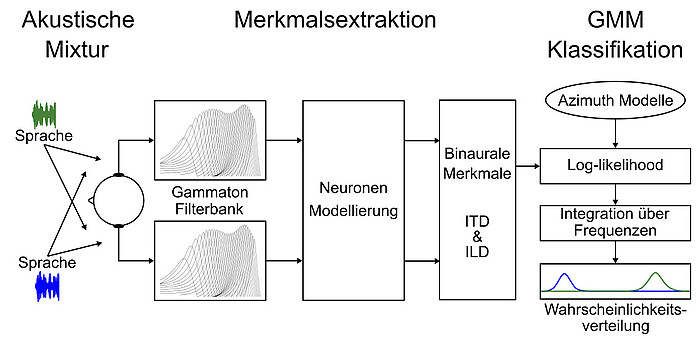

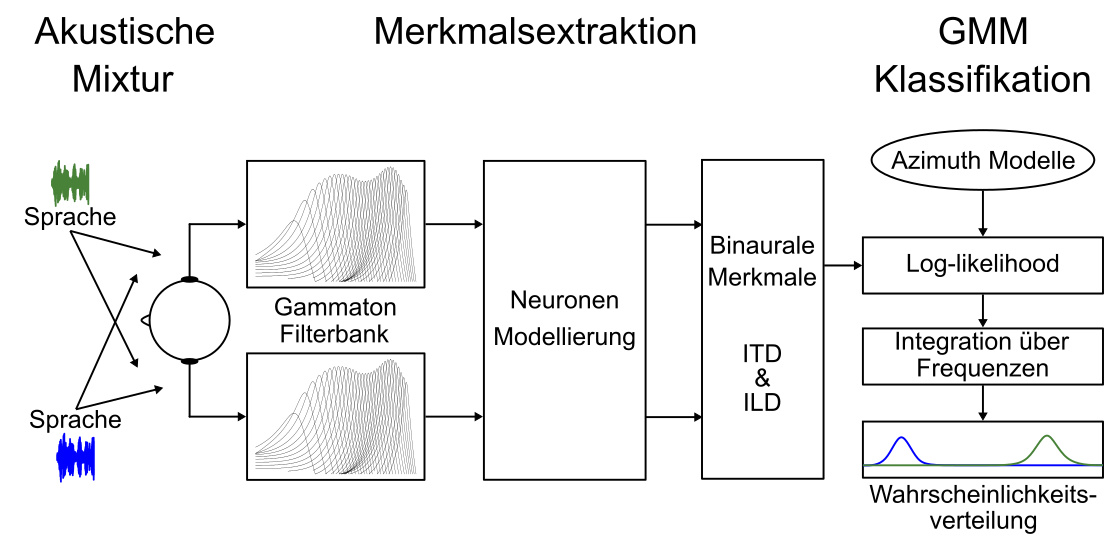

Gleichzeitig erfordern moderne und leistungsfähige Algorithmen für digitale Hörhilfen eine hohe Rechenleistung. Diesen Bedarf an leistungsfähigen und extrem verlustleistungsarmen Prozessorarchitekturen für digitale Hörhilfen wird das Projekt Smart HeaP adressieren. Hierzu wird eine vollständig programmierbare ASIP (Application Specific Instruction Set Processor) Architektur konzipiert und implementiert. Diese Prozessorarchitektur wird auf einer Audio-ASIP-Architektur basieren und wird durch gezielte Instruktionssatz-Erweiterungen und gezieltes Akzelerator-Design auf den Bedarf moderner leistungsfähiger Algorithmen angepasst. Durch die Verwendung einer Entwurfsumgebung wird der zu entwickelnde Chip vollständig Hochsprachen-programmierbar sein und so algorithmische Weiterentwicklungen ermöglichen.

Das wesentliche Ziel, die Erreichung einer extrem geringen Leistungsaufnahme, wird durch die Verwendung einer 22 nm FDSOI (Fully Depleted Silicon on Insulator) Technologie möglich gemacht. Der neuartige Einsatz dieser Halbleitertechnologie in Hörgeräte-Prozessoren führt beispielsweise zu drastisch reduzierten Leakage-Strömen und daher zu einer signifikant reduzierten Verlustleistungsaufnahme. Der finale Chip wird als Mixed-Signal ASIC-Design integriert, der neben dem ASIP-Prozessorkern weitere Komponenten wie AD/DA-Wandler und Kommunikationsmodule wie Bluetooth-Low-Energy enthält.

Der finale Hörgeräte-Chip wird in ein Demonstrator-Hörgerät integriert.

Am Fachgebiet Architekturen und Systeme des Instituts für Mikroelektronische Systeme wird die applikationsspezifische Instruktionssatzerweiterbarkeit und die Abbildung von leistungsfähigen Hörgeräte-Algorithmen auf die ASIP Architektur erforscht.

Beschreibung auf der Seite des Bundesministerium für Bildung und Forschung: