Prof. Dr.-Ing. Erich Barke

Prof. Dr.-Ing. Erich Barke

Telefon

Adresse

Appelstraße 4

30167 Hannover

30167 Hannover

Gebäude

Raum

Prof. Dr.-Ing. Erich Barke

Telefon

-

Publikationsliste

Konferenzbeiträge

-

(2018): STP - A Quadratic VLSI Placement Tool Using Graphic Processing Units, 17th International Symposium on Parallel and Distributed Computing, ISPDC, pp. 77-84 Weitere Informationen

DOI: 10.1109/ISPDC2018.2018.00020 -

(2018): Parallelization Strategies for the Detailed Routing Step, Analog 2018; 16th GMM/ITG-Symposium, VDE

ISBN: 978-3-8007-4754-2 -

(2016): Knowing your AMS system's limits: system acceptance region exploration by using automated model refinement and accelerated simulation, Forum on Specification and Design Languages (FDL)

DOI: 10.1109/FDL.2016.7880383 -

(2016): Modeling of Linear Stimuli for Accelerated Mixed-Signal Simulations, 15. ITG/GMM Fachtagung ANALOG 2016, Verifikation von Schaltungen und Systemen für das Internet der Dinge, Bremen, Germany Weitere Informationen

ISBN: 978-3-8007-4265-3 -

(2016): Embedded tutorial: Analog-/mixed-signal verification methods for AMS coverage analysis, 2016 Design, Automation & Test in Europe Conference & Exhibition (DATE) Weitere Informationen

-

(2015): Fast Global Interconnnect Driven 3D Floorplanning, VLSI-SoC

DOI: 10.1109/VLSI-SoC.2015.7314436 -

(2015): Analog Mixed-Level Modeling for Accelerated Simulation to Increase the Analog Coverage, FDL 2015, Forum on specification & Design Languages, Barcelona, Special Session "Towards Analog-/Mixed-Signal Coverage"

-

(2015): Split and Merge Strategies for Solving Uncertain Equations Using Affine Arithmetic, Proceedings of the SIMUTOOLS 2015

DOI: 10.4108/eai.24-8-2015.2260594 -

(2015): Automated Generation of Hybrid System Models for Reachability Analysis of Nonlinear Analog Circuits, Design Automation Conference (ASP-DAC), 2015 20th Asia and South Pacific, pp.725,730

DOI: 10.1109/ASPDAC.2015.7059096

ISBN: 978-1-4799-7790-1 -

(2014): Variation-Aware Behavioral Models of Analog Circuits Using Support Vector Machines with Interval Parameters, Computer Science and Electronic Engineering Conference (CEEC), 2014 6th

DOI: 10.1109/CEEC.2014.6958566 -

(2014): Simulation Based Verification with Range Based Signal Representations for Mixed-Signal Systems, SBCCI

DOI: 10.1145/2660540.2661010

ISBN: 978-1-4503-3156-2 -

(2014): Intervallwertige Support Vector Machines zur Verhaltensmodellierung analoger Schaltungen mit Parametervariationen , Tagungsband Analog2014

ISBN: 978-3-8007-3638-6 -

(2014): Application of Mission Profiles to Enable Cross-Domain Constraint-Driven Design, DATE, 1-6

DOI: 10.7873/DATE.2014.079 -

(2013): Analysis and Modeling of Minority Carrier Injection in Deep-Trench Based BCD Technologies, 9th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME 2013), (245-248)

DOI: 10.1109/PRIME.2013.6603160 -

(2013): Verification of Mixed-Signal Systems with Range Based Signal Representations, Frontiers in Analog CAD 2013 (FAC 2013)

-

(2013): Lösungsverfahren für nichtlineare implizite Gleichungssysteme unter Verwendung von Affiner Arithmetik und Gebietsaufteilungen , ANALOG 2-1, VDE-Verlag

ISBN: 978-3-8007-3467-2 -

(2013): Generation of Piecewise-Linear Semiconductor Models for Accelerated Mixed-Signal Simulation, Frontiers in Analog CAD 2013 (FAC 2013) Weitere Informationen

-

(2012): Enclosing the Modeling Error in Analog Behavioral Models Using Neural Networks and Affine Arithmetic, International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design 2012 (SMACD 2012), (5-8)

DOI: 10.1109/SMACD.2012.6339403 -

(2012): 3D Floorplanning Considering Vertically Aligned Rectilinear Modules Using T∗-tree, IEEE International 3D Systems Integration Conference (3DIC), 2-1, (1-5)

DOI: 10.1109/3DIC.2012.6263030 -

(2012): Efficient Generation of Analog Circuit Models for Accelerated Mixed-Signal Simulation, IEEE International System-on-Chip Conference 2012 (SOCC 2012), (104-109)

DOI: 10.1109/SOCC.2012.6398386

ISBN: 978-1-4673-1294-3 -

(2011): Fast Mixed-Signal Simulation using SystemC, IEEE International Systems Conference 2011 (SysCon 2011)

DOI: 10.1109/SYSCON.2011.5929046 -

(2011): Optimization of Chip Design Processes, African Conference on Software Engineering and Applied Computing

-

(2011): A Theoretical Probabilistic Simulation Framework for Dynamic Power Estimation, The 2011 International Conference on Computer-Aided Design (ICCAD 2011), (708-715)

DOI: 10.1109/ICCAD.2011.6105407 -

(2011): Anwendung der affinen Arithmetik auf das BSIMSOI-Modell zur Simulation von Parameterschwankungen, ANALOG 2-1, VDE-Verlag, (S. 49-54)

ISBN: 978-3-8007-3369-9 -

(2011): Using Analog Circuit Behavior to Generate SystemC Events for an Acceleration of Mixed-Signal Simulation, IEEE International Conference on Computer Design 2011 (ICCD 2011)

DOI: 10.1109/ICCD.2011.6081384 -

(2010): An Accelerated Mixed-Signal Simulation Kernel for SystemC, Forum on Specification & Design Languages 2010 (FDL)

DOI: 10.1049/ic.2010.0158 -

(2010): SystemC Mixed-Signal and Mixed-Level Simulation using an Accelerated Analog Simulation Approach, The International Workshop on Symbolic and Numerical Methods, Modeling and Applications to Circuit Design 2010 (SM2ACD)

DOI: 10.1109/SM2ACD.2010.5672303 -

(2010): Performance Management and Optimization of Semiconductor Design Projects, IAENG Transactions on Engineering Technologies Volume 4: Special Edition of the World Congress on Engineering and Computer Science 2-1, American Institute of Physics (AIP)

DOI: 10.1063/1.3460248 -

(2010): Optimization of Chip Design Processes using Task Graphs, International Conference on Software Technology and Engineering (ICSTE 2010)

DOI: 10.1109/ICSTE.2010.5608900 -

(2010): Integriertes Einfügen von Repeatern während der Platzierung, edaWorkshop10, VDE-Verlag

ISBN: 978-3-8007-3252-4 -

(2010): Beschleunigte Simulation von Mixed-Signal-Schaltungen der Automobilindustrie auf der Grundlage automatisch generierter Modelle, Analog 2-1, VDE-Verlag

ISBN: 978-3-8007-3224-1 -

(2009): Fast Dynamic Power Estimation Considering Glitch Filtering, IEEE International SOC Conference (SOCC 2009), (361-364)

DOI: 10.1109/SOCCON.2009.5398019 -

(2009): Efficient and Fast Analysis of Power Distribution Networks, IEEE Symposium on Industrial Electronics & Applications (IEEE ISIEA 2009), (425-430)

DOI: 10.1109/ISIEA.2009.5356442 -

(2009): Chip-Level Analysis of Power Distribution Networks, IEEE Regional Symposium on Micro and Nano Electronics (IEEE-RSM2009), (440-446)

-

(2009): Modeling and Simulation Techniques for Voltage Drop due to Multiple Input Switching Transitions, International Conference on Computer and Electrical Engineering (ICCEE 2009), (546-550)

DOI: 10.1109/ICCEE.2009.242 -

(2009): The Praise Approach For Accelerated Transient Analysis Applied To Wire Models, International Behavioral Modeling and Simulation Conference (BMAS)

DOI: 10.1109/BMAS.2009.5338876 -

(2009): An Approach for Analyzing and Evaluating Semiconductor Design Projects, International Conference on Systems Engineering and Engineering Management (ICSEEM'09)

-

(2009): Adrenalin - Simulating Chip Design Processes, University Booth at DATE '09

-

(2008): On Modeling and Simulating Chip Design Processes: The RS Model, IEEE International Engineering Management Conference - Europe, (81-85)

-

(2008): Towards Simulation of Chip Design Processes: The Request Service Model, IASTED International Conference on Modelling and Simulation, Quebec, Canada, (193-198)

-

(2008): A Trapezoidal Approach to Corner Stitching Data Structures for Arbitrary Routing Angles, IEEE Workshop on Design and Diagnostics of Electronic Circuits and Systems, (54-58)

-

(2008): Circuit Simulations with Uncertainties using Affine Arithmetic and Piecewise Affine Statemodels, Proceedings of International Conference on Solid-State and Integrated-Circuit Technology, IEEE Press

ISBN: 978-1-4244-2186-2 -

(2008): Verlässliche Modellierung integrierter analoger Schaltungen durch stückweise affine Abbildungen, 10. GMM/ITG-Fachtagung Analog 2-1, (56), VDE/VDI-Gesellschaft, VDE Verlag GmbH

-

(2008): Considering Possible Opens in Wire Delay Calculation for Non-tree Topologies, ACM Great Lakes Symposium on VLSI Proceedings, ACM Great Lakes Symposium on VLSI Proceedings, Association for Computing Machinery, (17-22)

ISBN: 978-1-59593-999-9 -

(2008): Distribution Arithmetic for Stochastical Analysis, Proceedings of the ASP-DAC 2-1, (537-542)

-

(2008): AC-Analyse analoger Schaltungen mit affiner Arithmetik, Analog 2-1, Entwicklung von Analogschaltungen mit CAE-Methoden, GMM/ITG, VDE (63-68)

ISBN: 978-3-8007-3083-4 -

(2008): Analog Circuit Simulation Using Range Arithmetics, Proceedings of the ASP-DAC 2-1, (762-767)

ISBN: 978-1-4244-1921-0 -

(2008): Redundanz in Repeaternetzwerken auf ULSI-Chips zur Erhöhung der funktionalen und parametrischen Ausbeute, 2. GMM/GI/ITG-Fachtagung "Zuverlässigkeit und Entwurf", VDE Verlag (8)

ISBN: 978-3-8007-3119-0 -

(2008): Applying Performance Management on Semiconductor Design Processes, IEEE International Conference on Industrial Engineering and Engineering Management, 2008. IEEM 2008., (278 - 281)

-

(2008): Methodologies for high-level modelling and evaluation in the automotive domain, Forum on Specification, Verification and Design Languages, 2008 (FDL 2008)

-

(2008): Automatic data extraction: A prerequisite for productivity measurement, Engineering Management Conference, 2008 (IEMC Europe 2008)

-

(2008): Simulation analoger Schaltungen mit affiner Arithmetik, 2. GMM/GI/ITG-Fachtagung "Zuverlässigkeit und Entwurf", VDE Verlag

-

(2007): Robust Wiring Networks for DfY Considering Timing Constraints, Great Lakes Symposium on VLSI 2-1, ACM, New York (43-48)

ISBN: 9781595936059 -

(2007): Verwendung von Gebietsarithmetiken zum Entwurf robuster Schaltungen und Systeme, 1.GMM/GI/GI-Fachtagung Zuverlaessigkeit und Entwurf, VDE Verlag, Berlin (131-136)

ISBN: 9783800730230 -

(2007): Erhoehung der Ausbeute durch robuste Verdrahtungsnetzwerke, 1.GMM/GI/GI-Fachtagung Zuverlaessigkeit und Entwurf, VDE Verlag GmbH - Berlin, Offenbach (117-123)

ISBN: 9783800730230 -

(2007): Ein Verfahren zur Analyse der Prozessschwankungen für nichtlineare Schaltungen mit nicht-Gauss-verteilten Parametern, 1.GMM/GI/ITG-Fachtagung Zuverlaessigkeit und Entwurf, VDE VERLAG GMBH, Berlin (25-30)

ISBN: 9783800730230 -

(2007): Corner-Stitching-Datenstruktur für beliebige Layoutstrukturen, EDA Workshop 2-1, VDE (41 - 46)

ISBN: 9783800730384 -

(2007): Incremental Fault Emulation, 17th International Conference on Field Programmable Logic and Applications, Delft University of Technology, Delft (542-545)

ISBN: 1424410606 -

(2007): Modellierung von Komplexität und Qualität als Faktoren von Produktivität in Design-Flows für integrierte Schaltungen

-

(2007): Building up a Performance Measurement System to Determine Productivity Metrics of Semiconductor Design Projects, IEEE International Engineering Management Conference (IEMC), Austin Texas, IEEE, IEEE (CD-ROM Proceedings)

ISBN: 978-1-4244-2146-6 -

(2007): Range Arithmetics to Speed up Reachability Analysis of Analog Systems, FDL 2-1, (CD-ROM)

-

(2007): CMCal: An Accurate Analytical Approach for the Analysis of Process Variations with Non-Gaussian Parameters and Nonlinear Functions, Design, Automation and Test in Europe (DATE2007), IEEE Catalog Number 07EX1635 (243 - 248)

ISBN: 9783981080124 -

(2007): Timing-Driven-3D-Platzierung mit einem kräftebasierten Ansatz, 1.GMM/GI/GI-Fachtagung Zuverlaessigkeit und Entwurf, VDE Verlag GmbH, Berlin (187-188)

ISBN: 9783800730230 -

(2007): Efficient modeling techniques for dynamic voltage drop analysis, Proceedings of the 44th annual Design Automation Conference (DAC) 2-1, (706-711)

ISBN: 978-1-59593-627-1 -

(2006): An Approach to Make Semiconductor Design Projects Comparable, 7th Asia Pacific Industrial Engineering and Management Systems Conference (APIEMS 2006), Asian Institute of Technology (CD-ROM)

ISBN: 974-8257-26-6 -

(2006): Computer Aided HRM for the Semiconductor Industry: Computer Aided HRM for the Semiconductor Industry: Limits and Perspectives, 7th Asia Pacific Industrial Engineering and Management Systems Conference (APIEMS 2006), (CD_ROM)

-

(2006): Global Routing for Force Directed Placement, Proceedings 10th IEEE Workshop on Signal Propagation on Interconnects (SPI06), IEEE (25-29)

ISBN: 1424404541 -

(2006): RL-Analysis of Meander Shaped Adjustment Modules, 10th IEEE Workshop on Signal Propagation on Interconnects

-

(2006): PARSIFAL: A Generic and Configurable Fault Emulation Environment with Non-Classical Fault Models, 16th International Conference on Field Programmable Logic and Applications, Publidisa, Madrid (241-246)

ISBN: 142440312X -

(2006): A Fast and Accurate Monte Carlo Method for Interconnect Variation, ICICDT 2006 Proceedings, (207-210)

-

(2006): Global Loops on ULSI Routing for DfY, ICICDT 2006 Proceedings, Padova, IEEE (179-182)

ISBN: 1424400988 -

(2006): Vermeidung fehlerhafter Verifikations-Ergebnisse beim Äquivalenz-Vergleich nichtlinearer analoger Schaltungen, 9. Workshop: Methoden und Beschreibungssprachen zur Modellierung und Verifikation von Schaltungen und Systemen (MBMV), saxOprint, Dresden (122-131)

ISBN: 3981028716 -

(2006): Semi-Symbolic Modeling and Simulation of Circuits and Systems, IEEE International Symposium on Circuits and Systems (ISCAS 2006), IEEE, Kos (CD-ROM)

ISBN: 0-7803-9390-2 -

(2006): Ein Verfahren zur effizienten Analyse von Schaltungen mit Parametervarianzen, 9. Workshop: Methoden und Beschreibungssprachen zur Modellierung und Verifikation von Schaltungen und Systemen (MBMV), Fraunhofer IIS (181-190)

ISBN: 3-9810287-1-6 -

(2005): A Methodology for Modeling Lateral Parasitic Transistors in Smart Power ICs, 2005 IEEE International Behavioral Modeling and Simulation Conference, IEEE (19-24)

ISBN: 078039352x -

(2005): Measure your Design Value to Improve It, IEEE International Engineering Management Conference. St. John's, Newfoundland, Kanada CD-ROM, Proceedings of 2005 IEEE International Engineering Management Conference, Newfoundland & Labrador, Canada.

ISBN: 0780391403 -

(2005): Detailed Routing With Integrated Static Timing Analysis Applying Simulated Annealing, Proceedings of the IEEE Northeastern Workshop on Circuits and Systems, IEEE (387-390)

ISBN: 0780389344 -

(2005): Time Constrained Verification of Analog Circuits using Model-Checking Algorithms, ENTCS, ETAPS 2005

-

(2005): Routing of Analog Busses with Parasitic Symmetry, International Symposium on Physical Design, ACM Press, New York (14-19)

ISBN: 1-59593-021-3 -

(2005): Net order optimization in analog net bundles, Microtechnologies for New Millenium 2005

-

(2005): Verifikation von Zeitbedingungen analoger Schaltungen durch Model-Checking-Verfahren, Analog 2005: 8. ITG/GMM-Diskussionssitzung Entwicklung von Analogschaltungen mit CAE-Methoden, (159-164)

-

(2005): Symbolische Analyse nichtlinearer analoger Schaltungen mit Hilfe Branch-and-Bound-optimierter Vereinfachung, ANALOG'05 (8. GMM/ITG-Diskussionssitzung), VDE, Berlin (253-258)

ISBN: ISBN 3800728818 -

(2005): PARSY: PARasitenSYmmetrische Verdrahtung für analoge Busse mit Modulgeneratoren, ANALOG'05 (8. GMM/ITG-Diskussionssitzung), VDE Verlag GmbH, Berlin, Offenbach (283-288)

ISBN: 3-8007-2881-8 -

(2005): Äquivalenz-Vergleich nichtlinearer analoger MIMO-Systeme mit automatischer Schrittweitensteuerung, Analog 2005: 8. ITG/GMM-Diskussionssitzung Entwicklung von Analogschaltungen mit CAE-Methoden, VDE-Verlag, Berlin (183-188)

ISBN: 3800728818 -

(2005): An Automated Approach to Measure Design Productivity Based on Quality Metrics in a Semiconductor Design Process, Asia Pacific Industrial Engineering and Management Society Conference, Manila (Philippines), (CD-ROM)

-

(2005): Modeling Substrate Currents in Smart Power ICs, Int. Symp. on Power Semiconductor Devices and ICs 2005 (ISPSD05), IEEE (127-130)

ISBN: 0-7803-8889-5 -

(2004): Placement Using a Localization Probability Model (LPM), Proceedings Design, Automation and Test in Europe (DATE2004), IEEE Computer Society, Los Alamitos (1412-1413)

ISBN: 0769520855 -

(2004): Hierarchical Automatic Behavioral Model Generation of Nonlinear Analog Circuits based on Nonlinear Symbolic Techniques, Proceedings Design, Automation and Test in Europe (DATE2004), IEEE Computer Society, Los Alamitos (442-447)

ISBN: 0769520855 -

(2004): Wirelength Reduction Using 3-D Physical Design, PATMOS 2-1, (453-462)

-

(2003): Dimensionierung analoger Schaltungen mit formalen Methoden, 7. ITG/GMM-Diskussionssitzung Entwicklung von Analogschaltungen mit CAE-Methoden, VDE-Verlag, Berlin (135-140)

ISBN: 3-8007-2778-1 -

(2003): Substrate Modeling and Noise Reduction in Mixed-Signal Circuits, Proc. of IFIP VLSI SoC, Darmstadt (13-18)

ISBN: 3901882170 -

(2003): Placing Substrate Contacts into Mixed-Signal Circuits Controlling Circuit Performance, Proc. Of 25th IEEE Custom Integrated Circuits Conference, (373-376)

-

(2003): 3-D Placement Considering Vertical Interconnects, Proceedings of the IEEE International SOC Conference, (257-258)

ISBN: 0780381823 -

(2003): LIFT: Ein Multi-Layer IC Floorplanning Tool, 11. E.I.S.-Workshop: Entwurf Integrierter Schaltungen und Systeme, VDE Verlag GmbH (157-162)

ISBN: 3800727609 -

(2003): Ein neues Platzierungsverfahren für einen leitbahnzentrierten Designflow, E.I.S.-Workshop, VDE VERLAG GmbH (151-156)

ISBN: 3800727609 -

(2002): A Direct Mapping System for Datapath Module and FSM Implementation into LUT-Based FPGAs, D.A.TE 2002: 5th Design Automation and Test in Europe, IEEE Computer Society (1085)

ISBN: 0769514715 -

(2002): A New Placement Algorithm for an Interconnect Centric Design Flow, ASIC/SOC 2-1, IEEE Press (416-420)

ISBN: 0780374940 -

(2002): Analog Circuit Sizing Based on Formal Methods Using Affine Arithmetic, ICCAD 2-1, IEEE Computer Society (486-489)

ISBN: ISBN 0780376072 -

(2002): On Discret Modeling and Model Checking for Nonlinear Analog Systems, CAV 2002: Conference on Computer-Aided Verification, Springer Verlag, Berlin

-

(2002): Betrachtungen zur Simulationsgeschwindigkeit von Verhaltensmodellen nichtlinearer integrierter Analogschaltungen, Analog 2-1, (107-112)

-

(2002): Model Checking Algorithms for Analog Verification, DAC 2002

-

(2002): An Approach to Model Checking for Nonlinear Analog Systems, Date 2-1, IEEE Computer Society, Los Alamitos (1080-1080)

ISBN: 0769514715 -

(2002): An Upper Bound for 3D Slicing Floorplans, Proceedings of 7th ASPDAC and 15th Int'l Conf. on VLSI Design (2002), IEEE Computer Society Press, Los Alamitos (567-572)

ISBN: 0769514413 -

(2002): "Parameter Controlled Automatic Symbolic Analysis of Nonlinear Analog Circuits", DATE2002: 5th Design Automation and Test in Europe, IEEE Computer Soc., Los Alamitos, CA (274-278)

ISBN: 0769514715 -

(2001): Automatic Analog Behavioral Model Generation, University Booth DATE2001: 4th Design Automation and Test in Europe

-

(2001): An Improved Hierarchical Classification Algorithm for Structural Analysis of Integrated Circuits, DATE2001: 4th Design Automation and Test in Europe, (807)

-

(2001): Architecture Driven Partitioning, DATE2001: 4th Design Automation and Test in Europe, (479-485)

-

(2001): Extraktion und Simulation parasitärer Substrateffekte an einer Mixed-Signal CMOS-Schaltung, 10. E.I.S.-Workshop: Entwurf integrierter Schaltungen (8. ITG-Fachtagung), (75-80)

-

(2001): Stromabhängige Verdrahtung von Analogschaltungen, 10. E.I.S.-Workshop: Entwurf integrierter Schaltungen (8. ITG-Fachtagung), (167-170)

-

(2001): PuMA++: A Fully Automatic Path from Specification to Multi-FPGA-Prototype, FPGA 01: International Conference on Field Programmable Gate Arrays

-

(2001): A Combined Structural and Symbolic Method for Automatic Behavioral Modeling of Nonlinear Analog Circuits, Proceedings of the 15th European Conference on Circuit Theory and Design (ECCTD 01), Helsinki University of Technology, Espoo, Finnland (II-229-232)

ISBN: 9512255731 -

(2001): A New Placement Method for Direct Mapping into LUT-Based FPGAs, FPL2001: 11th Conference on Field-Programmable Logic and Applications, (27-36)

-

(2001): CHIPDESIGN - A Novel Project-oriented Microelectronics Course, 2001 International Conference on Microelectronic Systems Education (MSE 2001), IEEE Computer Society, Los Alamitos, USA (71-72)

ISBN: 0769511562 -

(2000): Symbolic Analysis of Nonlinear Analog Circuits by Simplification of Nested Expressions, SMACD 2000: Proc. 7th Int. Workshop on Symbolic Methods and Applications in Circuit Design, (151-154)

-

(2000): PARCOURS - Substrate Crosstalk Analysis for Complex Mixed-Signal-Circuits, PATMOS 2000: 10th International Workshop, (306-315)

-

(2000): Static Timing Analysis Taking Crosstalking into Account, DATE 2000: 3th Design Automation and Test in Europe, (451-455)

-

(2000): Single Step Current Driven Routing of Multiterminal Signal Nets for Analog Applications, DATE 2000: 3th Design Automation and Test in Europe, (446-450)

-

(2000): An Optimised Partitioning and Mapping Environment for Rapid Prototyping of Structural RT-level Circuit Descriptions, DATE 00: 3rd Design Automation and Test in Europe, University Booth

-

(2000): A Current Driven Routing and Verification Methodology for Analog Applications, DAC 2000: 37th Design Automation Conference, (385-389)

-

(2000): Current Density Calculation of Integrated Circuit Interconnect, MICRO.tec 2000 Proceedings Volume 2, VDE Verlag, Berlin (77-81)

ISBN: 3800725797 -

(2000): CoMGen: Direct Mapping of Arbitrary Components into LUT-Based FPGAs, FPL2000: 10th Conference on Field-Programmable Logic and Applications, (191-200)

-

(1999): Ein Ansatz zur formalen Verifikation nichtlinearer statischer Analogschaltungen mit Parametertoleranzen, Analog 99: 5. GMM/ITG-Diskussionssitzung Entwicklung von Analogschaltungen mit CAE-Methoden, (93-94)

-

(1999): Ein neuer hierarchischer Klassifizierungsalgorithmus zur strukturellen Analyse integrierter Schaltungen, Analog 99: 5. GMM/ITG-Diskussionssitzung Entwicklung von Analogschaltungen mit CAE-Methoden, (77+78)

-

(1999): Dimensionierung analoger Schaltungen unter Verwendung intervallarithmetischer Verfahren, Analog 99: 5. GMM/ITG-Diskussionssitzung Entwicklung von Analogschaltungen mit CAE-Methoden, (87-88)

-

(1999): An Extended Bipolar Transistor Model For Substrate Crosstalk Analysis, SSCS 99: IEEE Custom Integrated Circuits Conference, (579-582)

-

(1999): Benchmarking von RLC-Netzwerkreduktionsverfahren, Analog 99: 5. GMM/ITG-Diskussionssitzung Entwicklung von Analogschaltungen mit CAE-Methoden, (145-146)

-

(1999): Using Term Ordering to Improve Symbolic Behavioral Model Generation of Nonlinear Analog Circuits, ECCTD99: European Conference on Circuit Theory and Design, (74-77)

-

(1999): Modélisation de couplage électromagnétique par le substrat pour la simulation des circuits intégrés, FTFC99: 2ème Journées Francophones d'études Faible Tension Faible Consommation, Recueil des Communications, (S.119-125)

-

(1999): Berechnung der Stromdichten des Leitbahnsystems integrierter Schaltungen, Analog 99: 5. GMM/ITG-Diskussionssitzung Entwicklung von Analogschaltungen mit CAE-Methoden, (52-53)

-

(1999): Modellierung von Übersprechen durch das Substrat für die Schaltungssimulation von integrierten Mixed-Signal-Schaltungen, Analog 99: 5. GMM/ITG-Diskussionssitzung Entwicklung von Analogschaltungen mit CAE-Methoden, (66+67)

-

(1999): Entwurf eines Testchips zur Messung parasitärer Effekte, Analog 99: 5. GMM/ITG-Diskussionssitzung Entwicklung von Analogschaltungen mit CAE-Methoden, (68+69)

-

(1999): A Case Study: Logic Emulation - Pitfalls and Solutions, RSP 99: 10th IEEE Workshop on Rapid System Prototyping, (160-163)

-

(1999): RIG: Targeting Designs with Embedded Memories to ASIC and FPGA Technologies, International Workshop on IP Based Synthesis and System Design, (237-240)

-

(1999): A Universal Module Generator for LUT-Based FPGAs, 10th IEEE Workshop on Rapid System Prototyping, (230-235)

-

(1998): A Formal Approach to Verification of Linear Analog Circuits with Parameter Tolerances, DATE 98: Design, Automation and Test in Europe

-

(1998): Accurate Junction Capacitance Modelling for Substrate Crosstalk Calculation, PATMOS 1998: 8th International Workshop, (297-306)

-

(1998): An Optimized Design Flow for Fast FPGA-Based Rapid Prototyping, FPL 98: 8th Int. Workshop on Field Programmable Logic and Applications, (79-88)

-

(1998): Real Time Fault Injection Using Logic Emulator, ASP-DAC 98: Asia and South Pasific Design Automation Conference 1998

-

(1998): A New Hierachical Graph Model for Multiple FPGA Partitioning, WDTA 98: IEEE Workshop on Design, Test and Application, (101-104)

-

(1998): Error Estimation on Symbolic Behavioral Models of Nonlinear Analog Circuits, SMACD 1998: 5th International Conference on Symbolic Methods and Applications to Circuits Design

-

(1997): Modellierung und Simulation von Substratkoppelungen in bipolaren integrierten Schaltungen, Mikroelektronik 97, (61-66)

-

(1997): Design Driven Partitioning, ASP-DAC 97: 2nd Asia and South Pacific Design Automation Conference

-

(1997): An Universal Booth-Multiplier Generator for SRAM-Based FPGAs, FPGA 97: 5th International Symposium on Field-Programmable Gate Arrays

-

(1997): A Universal Pezaris Array Multiplier Generator for SRAM-Based FPGAs, ICCD 97: International Conference on Computer Design, (489-495)

-

(1997): A New Approach to Fault Emulation, RSP 97: 8th IEEE International Conference on Rapid Systems Prototyping, (173-179)

-

(1997): Das allgemeine Problem der falscher Pfade: Ein Überblick, 4. SICAN Herbsttagung, (227-232)

-

(1996): Speeding Up Parallel Layout Verification by Simulation-Based Task Scheduling, ESS 96: 8th European Simulation Symposium

-

(1996): Hierarchical Partitioning, ICCAD 96: Int. Conference on Comuter Aided Design, (470-477)

-

(1996): Circuit Partitioning Using High-Level Design Information, IDPT 96: 2nd World Conference on Integrated Design & Process Technology, (256-266)

-

(1996): An Universal CLA Adder Generator for SRAM-Based FPGAs, FPL 96: 6th Int. Workshop on Field-Programmable Logic and Applications, (44-54)

-

(1996): PALACE: A Parallel and Hierarchical Layout Analyzer and Circuit Extractor, ED&TC 96: European Design and Test Conference, (357-361)

-

(1996): Equation-Based Behavioral Model Generation for Nonlinear Analog Circuits, DAC 96: 33rd Design Automation Conference, (236-239)

-

(1995): A Formal Approach to Nonlinear Analog Circuit Verification, ICCAD 95: Int. Conference on Computer Aided Design, (123-127)

-

(1995): Ein Verfahren zur Verifikation nichtlinearer analoger Schaltungen, 2. ITG-Diskussionssitzung Neue Anwendungen theoretischer Konzepte in der Elektrotechnik, (145-147)

-

(1994): Integration der Monte-Carlo-Analyse in eine Schaltungsumgebung, 3. GI/ITG/GME-Fachtagung Rechnergestützter Entwurf und Architektur mikroelektronischer Systeme, (96-104)

-

(1993): Verhaltensmodell und Simulation eines Radio-Koinzidenzdemodulator, 2. GME/ITG Diskussionssitzung Entwicklung von Analogschaltungen mit CAE-Methoden, (114-118)

-

(1993): Reduktion parasitärer RC-Netzwerke in höchstintegrierten Schaltungen, 6. E.I.S.- Workshop, (361-368)

Journalbeiträge

-

(2018): Hierarchical Verification of AMS Systems With Affine Arithmetic Decision Diagrams, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, pp. 1–12 Weitere Informationen

DOI: 10.1109/TCAD.2018.2864238 -

(2008): Design of Robust Signal and Clock Networks, Proceedings in Applied Mathematics and Mechanics, Proceedings in Applied Mathematics and Mechanics(Volume 7, Issue 1), GAMM, Wiley InterScience (2)

DOI: 10.1002/pamm.200700468 -

(2006): Modeling Lateral Parasitic Transistors in Smart Power ICs, IEEE Transactions on Device and Materials Reliability, 6(3), IEEE (408-420)

DOI: 10.1109/TDMR.2006.881506

ISBN: 15304388 -

(1996): Bei Electronic Design Automation bleibt der Weg das Ziel, F&M, 104(6)

Sonstiges

-

(2016): Automated Refinement of Analog/Mixed-Signal SystemC Models by Non-Functional Effects, University Booth at DATE 2016, Design, Automation & Test in Europe Conference & Exhibition), Dresden, Germany. Weitere Informationen

Buchbeiträge

-

(2018): Knowing Your AMS System's Limits: System Acceptance Region Exploration by Using Automated Model Refinement and Accelerated Simulation, Languages, Design Methods, and Tools for Electronic System Design, Springer, pp. 1-14

DOI: 10.1007/978-3-319-62920-9

ISBN: 978-3-319-62919-3 -

(2012): Towards Abstract Analysis Techniques for Range Based System Simulation, System Specification and Design Languages, Selected Contributions from FDL, Volume 106, pp. 105-122, Springer

DOI: 10.1007/978-1-4614-1427-8_7

ISBN: 978-1-4614-1427-8 -

(2007): Improving Efficiency and Robustness of Analog Behavioral Models, Advances in Design and Specification Languages for Embedded Systems Selected Contributions from FDL'06, Sorin A. Huss, Springer Netherlands (53-68)

ISBN: 978140206147

Bücher

-

(2000): Integrated Circuit Design: Power and Timing Modeling, Optimization and Simulation (PATMOS 2000: Proceedings 10th International Workshop), Springer Verlag, Heidelberg

-

-

Forschungsprojekte

Electronic Design Automation

-

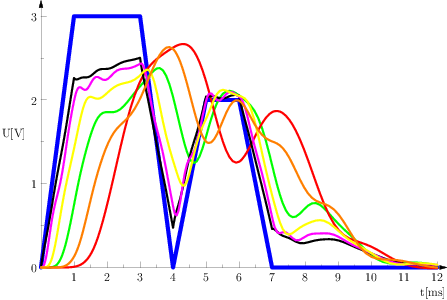

Neue Simulationsmethoden zur beschleunigten Mixed-Signal-SimulationDieses Forschungsprojekt basiert auf einem speziellen Ansatz zur beschleunigten Mixed-Signal-Simulation von analogen Schaltungsmodellen. Das Verfahren ist derzeit auf stückweise konstante Eingangserregungen optimiert. Eines der wesentlichen Ziele dieses Forschungsprojekts ist die Erweiterung der neuartigen Simulationsmethodik um die Berücksichtigung zusätzlicher Typen von Signaleingangserregungen.Leitung: Dr.-Ing. Markus Olbrich, Prof. Dr.-Ing. Erich BarkeTeam:Jahr: 2019Förderung: Deutsche Forschungsgemeinschaft (DFG): BA 812/24-1Laufzeit: März 2014 - September 2019

![]()

![]()

-

Parallelisierung von RoutingalgorithmenWerkzeuge zur Erzeugung der Verdrahtung für einen gegebenen Chip haben aufgrund der Komplexität dieses Problems sehr hohe Laufzeiten. Ziel dieses Forschungsprojektes ist die Beschleunigung dieses Vorgangs durch die Ausnutzung hochparalleler Architekturen, insbesondere Graphical Processing Units. Zu diesem Zweck sollen Algorithmen und Datenstrukturen gefunden werden, die eine effiziente Aufteilung des Problems auf eine große Anzahl an Recheneinheiten erlauben.Leitung: Dr.-Ing. Markus OlbrichTeam:Jahr: 2014

-

3D-FloorplanningDas Forschungsprojekt hat sich als Ziel gesetzt, geeignete Optimierungsverfahren und Datenstrukturen für das 3D-Floorplanning zu entwickeln, bzw. vorhandene Verfahren und Datenstrukturen an das 3D-Floorplanning anzupassen. Weiterhin soll untersucht werden welche Entwurfsziele beim 3D-Floorplanning von Bedeutung sind. Gegebenenfalls sollen neue Entwurfsziele definiert und in das Optimierungsverfahren integriert werden.Leitung: Dr.-Ing. Markus OlbrichTeam:Jahr: 2014Laufzeit: abgeschlossen

![]()

![]()

-

Verlässliche ModellierungZiel des Projektes ist die Erzeugung von Verhaltensmodellen, die Parameterabweichungen in der Originalschaltung berücksichtigen. Die Parameterabweichungen werden mit Hilfe der affinen Arithmetik dargestellt.Leitung: Prof. Dr.-Ing. Erich BarkeTeam:Jahr: 2014

![]()

![]()

-

Lösungsverfahren für semi-symbolische Analog-SimulationenDie Parameter von analogen Schaltungen sind im Allgemeinen nicht exakt bekannt, denn sie unterliegen Schwankungen durch den Herstellungsprozess, Alterung oder die Umgebungstemperatur. Am Institut für mikroelektronische Systeme wurde ein Analogschaltungssimulator entwickelt, der zur Simulation solcher Parameterschwankungen affine Arithmetik verwendet. Ziel dieses Projektes ist die Vergrößerung des Konvergenzbereiches durch Gebietsaufteilungen.Leitung: Prof. Dr.-Ing. Erich BarkeTeam:Jahr: 2014Laufzeit: Januar 2012 - Mai 2015

![]()

![]()

Rekonfigurierbare Architekturen

-

Schaltungsentwurf und physikalisches Design für eine neuartige FPGA-ArchitekturUntersuchung und Validierung der Machbarkeit und der erzielbaren Leistung eines neuartigen Field Programmable Gate Array (FPGA).Leitung: Prof. Dr.-Ing. H. Blume, apl. Prof. Dr.-Ing. G. Payá VayáTeam:Jahr: 2013Förderung: Bundesministerium für Bildung und ForschungLaufzeit: Mai 2013 - Juli 2014

![]()

![]()

-